### Contains pages for the

## **Maintenance Manual**

for

**AM/FM SIGNAL GENERATOR**

2023

&

2024

9 kHz - 1.2 GHz

9 kHz - 2.4 GHz

Part number 46882-245M Issue 3

Creation date 8-Sep-98

Please open and fit to the supplied Ring Binder

# AM/FM SIGNAL GENERATOR

2023

2024

9 kHz - 1.2 GHz

9 kHz - 2.4 GHz

#### Includes information on:

Option 1:

No attenuator.

Option 2:

DC operation.

Option 3:

High power.

Option 4:

High stability frequency standard.

Option 5:

Rear panel connectors. Fast pulse modulation.

Option 7: Option 10:

1 V peak mod input.

Option 11:

Fast pulse and high power.

Option 100: Internal pulse generator.

© IFR Ltd. 1998

No part of this book may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, or recorded by any information storage or retrieval system, without permission in writing by IFR Ltd.

Printed in the UK

Manual part no. 46882-245M Issue 3

8-Sep-98

### About this manual

This manual provides servicing information to a defined circuit area for the 2023 & 2024 AM/FM Signal Generators.

### Intended audience

The book is intended for qualified service engineers and assumes a knowledge of the instrument to a level covered in the Operating Manual 46882-225U.

### Structure

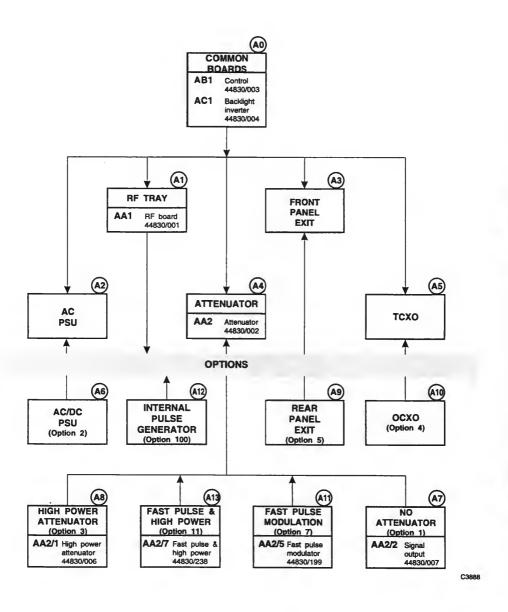

#### Chapter 1 Technical description

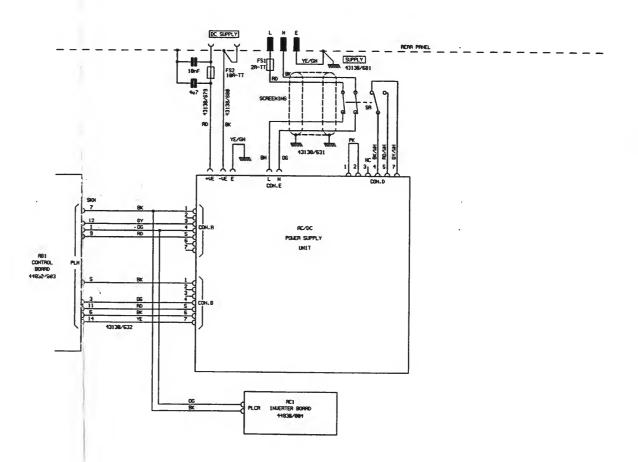

This includes block diagrams and detailed board circuit descriptions. The circuit descriptions refer directly to the servicing diagrams contained in Chapter 7.

#### Chapter 2 Maintenance

Refer to this chapter for board and unit access, service policy and routine safety testing and inspection.

#### Chapter 3 Adjustment procedures

Refer to this chapter for information on password use and adjustment procedures.

#### Chapter 4 Initial repair

What to do if the instrument shows no signs of life.

#### Chapter 5 Fault diagnosis

Based on error message reports and narrows the search down to a defined circuit area.

#### Chapter 6 Replaceable parts

Contains instrument and board component parts and a section on miscellaneous mechanical parts.

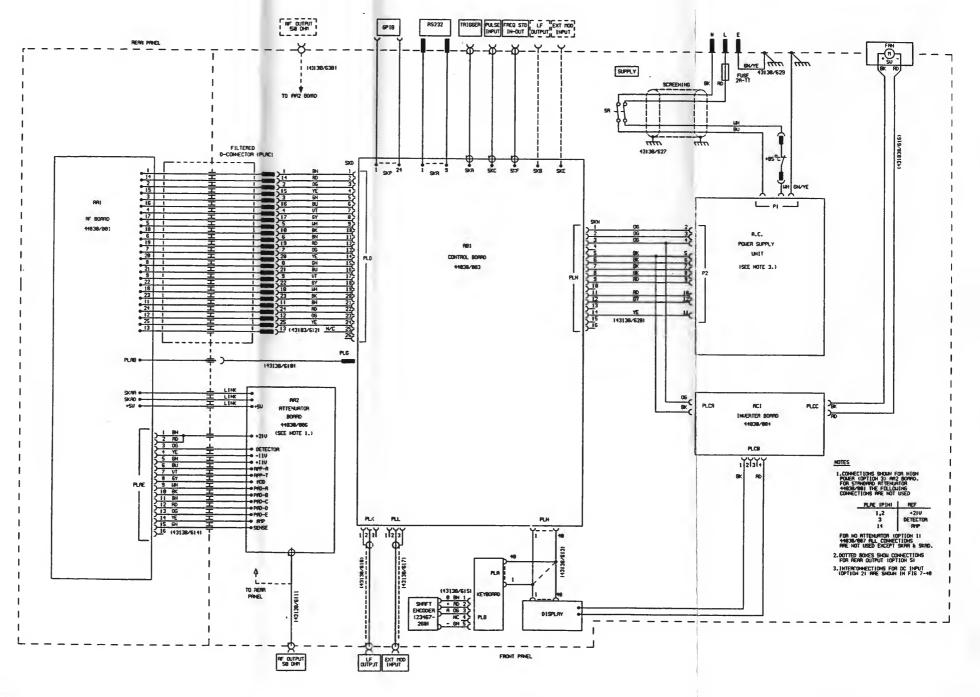

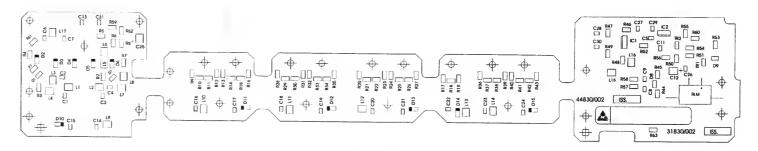

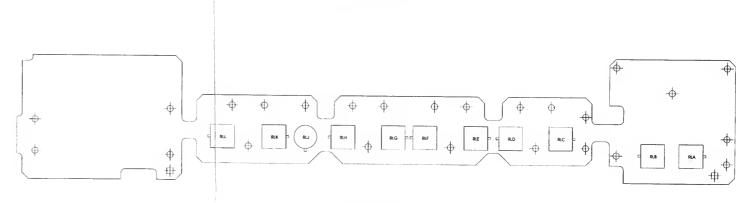

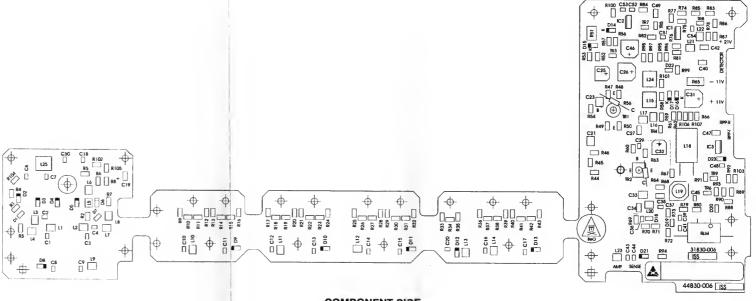

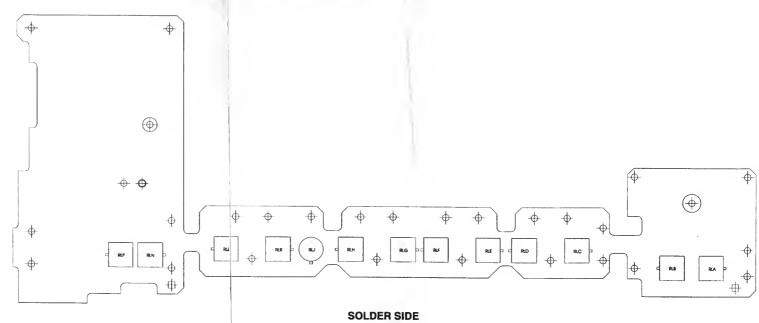

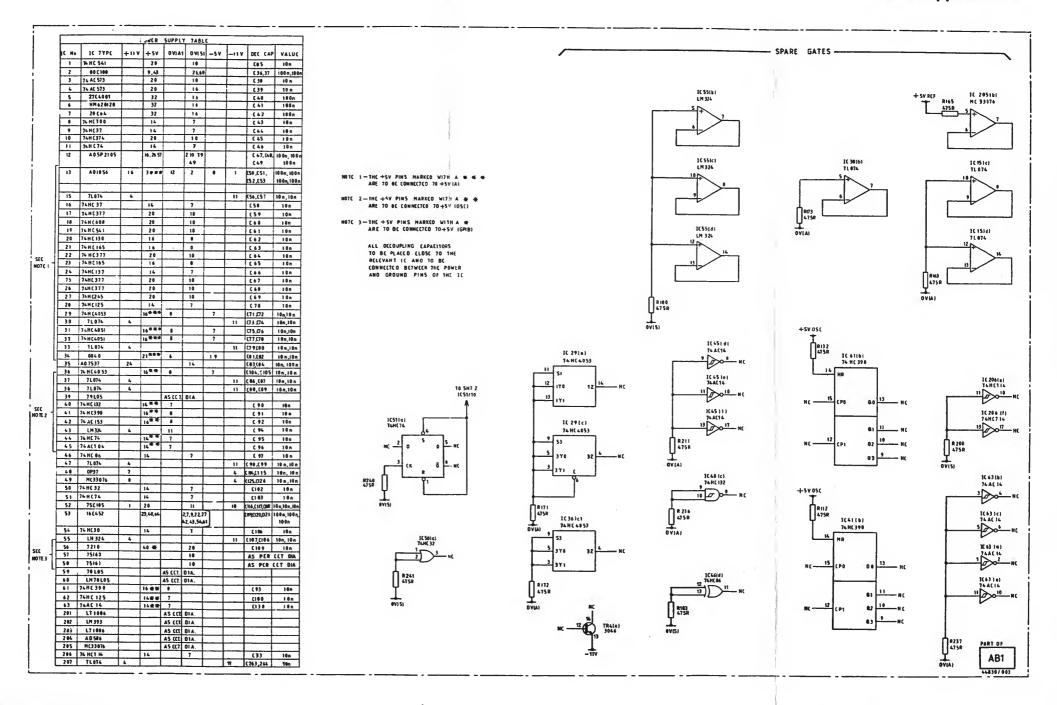

#### Chapter 7 Servicing diagrams

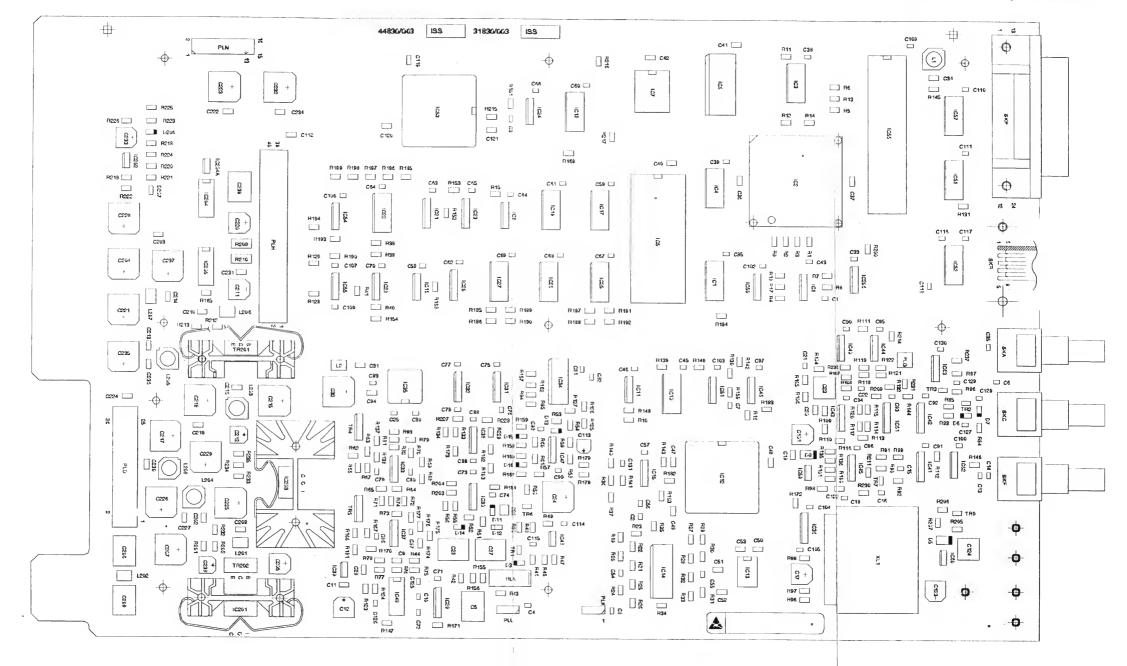

Contains interconnection drawings, board circuits and component layout diagrams.

### **Associated publications**

Refer to the Operating Manual 46882-225U for an up-to-date list of associated publications.

# Contents

| Precaution | S                                                                | iv  |

|------------|------------------------------------------------------------------|-----|

| Précaution | S                                                                | vii |

| Vorsichtsn | naßnahmen                                                        | ix  |

| Precauzion | ii                                                               | xi  |

|            | ıes                                                              |     |

| Chapter 1  | TECHNICAL DESCRIPTION                                            | 1-1 |

| Chapter 2  | MAINTENANCE                                                      | 2-1 |

| Chapter 3  | ADJUSTMENT PROCEDURES                                            | 3-1 |

|            | Adjustments                                                      | 3-4 |

|            | Recommended test equipment                                       |     |

|            | Adjustment procedures                                            |     |

|            | Adjustment procedures for instruments fitted with Option 3 or 11 |     |

|            | Adjustment procedure tables                                      |     |

| Chapter 4  | INITIAL REPAIR                                                   |     |

| Chapter 5  | FAULT DIAGNOSIS                                                  | 5-1 |

| Chapter 6  | REPLACEABLE PARTS                                                | 6-1 |

| Chapter 7  | SERVICING DIAGRAMS                                               | 7-1 |

|            | Circuit notes                                                    | 7-2 |

### **Precautions**

WARNING |

CAUTION

Note

These terms have specific meanings in this manual:

WARNING

Information to prevent personal injury.

CAUTION

Information to prevent damage to the equipment.

Note

Important general information.

### Symbols used on this product

The meaning of hazard symbols appearing on the equipment is as follows:-

**Symbol**

Nature of hazard

$\triangle$

General hazard

Dangerous voltage

Toxic hazard

Static-sensitive components

### General conditions of use

This product is designed and tested to comply with the requirements of IEC/EN61010-1 'Safety requirements for electrical equipment for measurement, control and laboratory use', for Class I portable equipment and is for use in a pollution degree 2 environment. The equipment is designed to operate from an installation category 1 and 2 supply.

Equipment should be protected from the ingress of liquids and precipitation such as rain, snow, etc. When moving the equipment from a cold to a hot environment, it is important to allow the temperature of the equipment to stabilise before it is connected to the supply to avoid condensation forming. The equipment must only be operated within the environmental conditions specified in Chapter 1 'Performance data' in the Operating manual, otherwise the protection provided by the equipment may be impaired.

This product is not approved for use in hazardous atmospheres or medical applications. If the equipment is to be used in a safety-related application, e.g. avionics or military applications, the suitability of the product must be assessed and approved for use by a competent person.

### WARNING

### Electrical hazards (AC supply voltage)

This equipment conforms with IEC Safety Class I, meaning that it is provided with a protective grounding lead. To maintain this protection the supply lead must always be connected to the source of supply via a socket with a grounded contact.

Be aware that the supply filter contains capacitors that may remain charged after the equipment is disconnected from the supply. Although the stored energy is within the approved safety requirements, a slight shock may be felt if the plug pins are touched immediately after removal.

#### **Fuses**

Note that the internal supply fuse is in series with the live conductor of the supply lead. If connection is made to a 2-pin unpolarized supply socket, it is possible for the fuse to become transposed to the neutral conductor, in which case, parts of the equipment could remain at supply potential even after the fuse has ruptured.

#### Removal of covers

Disconnect the supply before removing the covers so as to avoid the risk of exposing high voltage parts. If any internal adjustment or servicing has to be carried out with the supply on, it must only be performed by a skilled person who is aware of the hazard involved.

### WARNING

### Fire hazard

Make sure that only fuses of the correct rating and type are used for replacement.

If an integrally fused plug is used on the supply lead, ensure that the fuse rating is commensurate with the current requirements of this equipment. See under 'Performance data' in Chapter 1 in the Operating/Instruction manual for power requirements.

### **WARNING**

### **Toxic hazards**

Some of the components used in this equipment may include resins and other materials which give off toxic fumes if incinerated. Take appropriate precautions, therefore, in the disposal of these items.

### WARNING

### Beryllia

Beryllia (beryllium oxide) is used in the construction of the following components in this equipment:

TR808 on AA1;

TR1 and TR2 on AA2/1 and AA2/7.

This material, when in the form of fine dust or vapour and inhaled into the lungs, can cause a respiratory disease. In its solid form, as used here, it can be handled quite safely although it is prudent to avoid handling conditions which promote dust formation by surface abrasion.

Because of this hazard, you are advised to be very careful in removing and disposing of these components. Do not put them in the general industrial or domestic waste or despatch them by post. They should be separately and securely packed and clearly identified to show the nature of the hazard and then disposed of in a safe manner by an authorized toxic waste contractor.

### WARNING

### Beryllium copper

Some mechanical components within this instrument are manufactured from beryllium copper. This is an alloy with a beryllium content of approximately 5%. It represents no risk in normal use.

The material should not be machined, welded or subjected to any process where heat is involved. It must be disposed of as "special waste".

It must NOT be disposed of by incineration.

### CAUTION

### Static-sensitive components

The presence of static-sensitive components is indicated in the equipment by yellow disks, flags or labels bearing the symbol . Certain handling precautions should be observed to prevent these components being permanently damaged by static charges or fast surges:-

- 1. If a static-sensitive component is to be removed or replaced, the following anti-static equipment should be used:-

- A work bench with a grounded conductive surface.

- Metallic tools grounded either permanently or by repeated discharges.

- A low-voltage grounded soldering iron.

- A grounded wrist strap and a conductive grounded seat cover for the operator

whose outer clothing should not be of man-made fibre.

- If a printed board containing static-sensitive components (as indicated by warning disk or flag) is removed, it must be temporarily stored in a conductive plastic bag.

- 3. As a general precaution, avoid touching the leads of a static-sensitive component. When handling a new one, leave it in its conducting mount until it is required for use.

- 4. If using a freezer aerosol in fault finding, take care not to spray programmable ICs as this may affect their contents.

vi

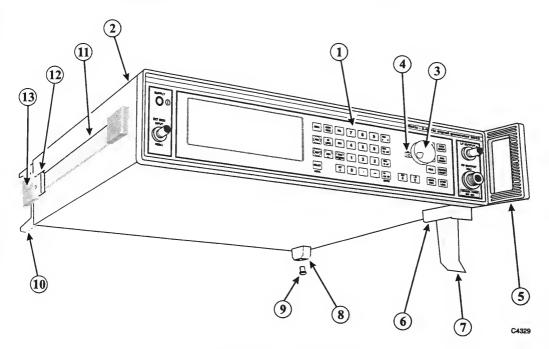

# Chapter 1 TECHNICAL DESCRIPTION

### **Contents**

| Introduction                                           |         |

|--------------------------------------------------------|---------|

| Synthesiser                                            |         |

| RF processing                                          | 1-4     |

| LF processing                                          |         |

| LF output                                              | 1-7     |

| AM and level control                                   | 1-7     |

| FM/φM                                                  | 1-7     |

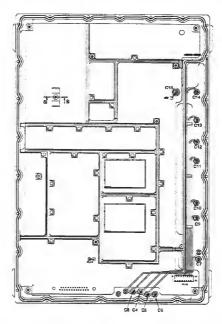

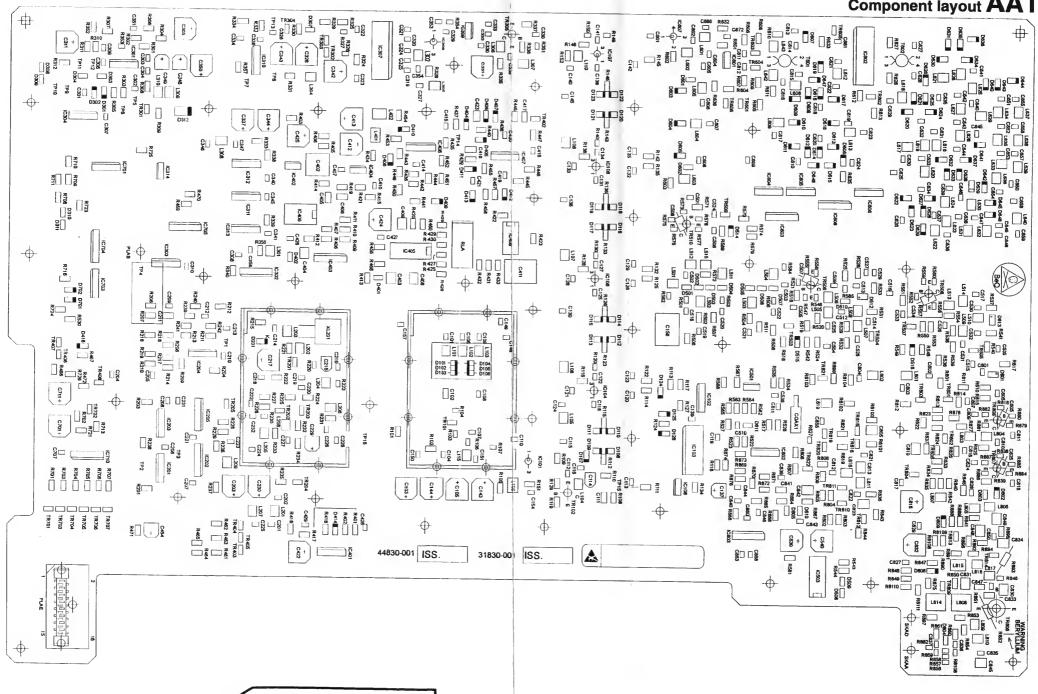

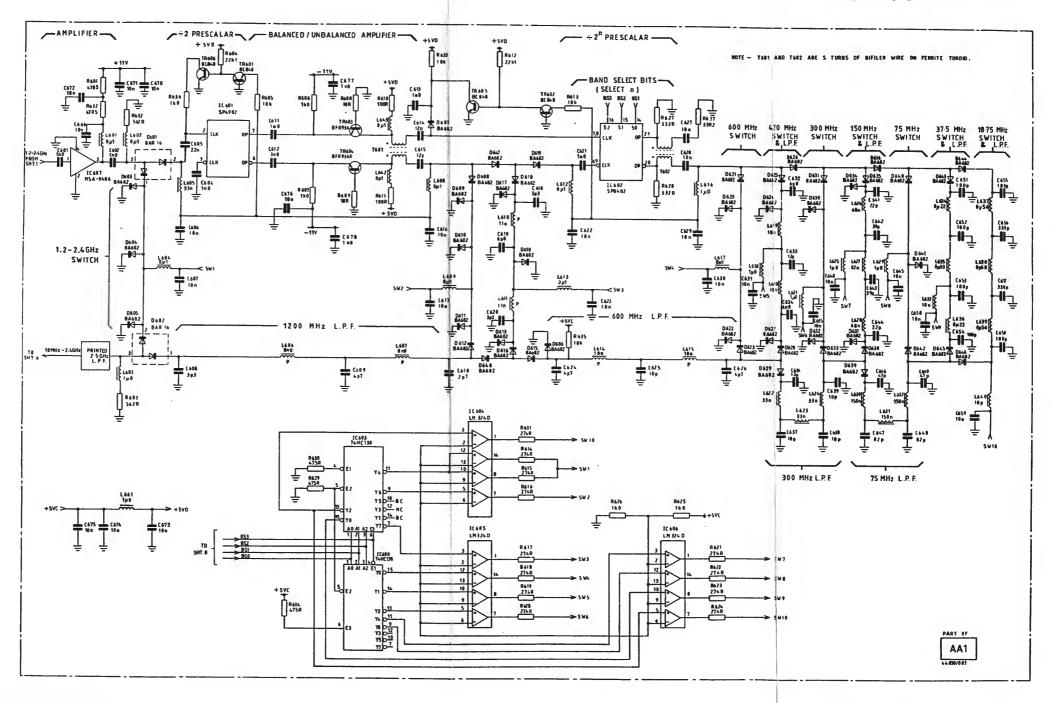

| RF board - AA1                                         |         |

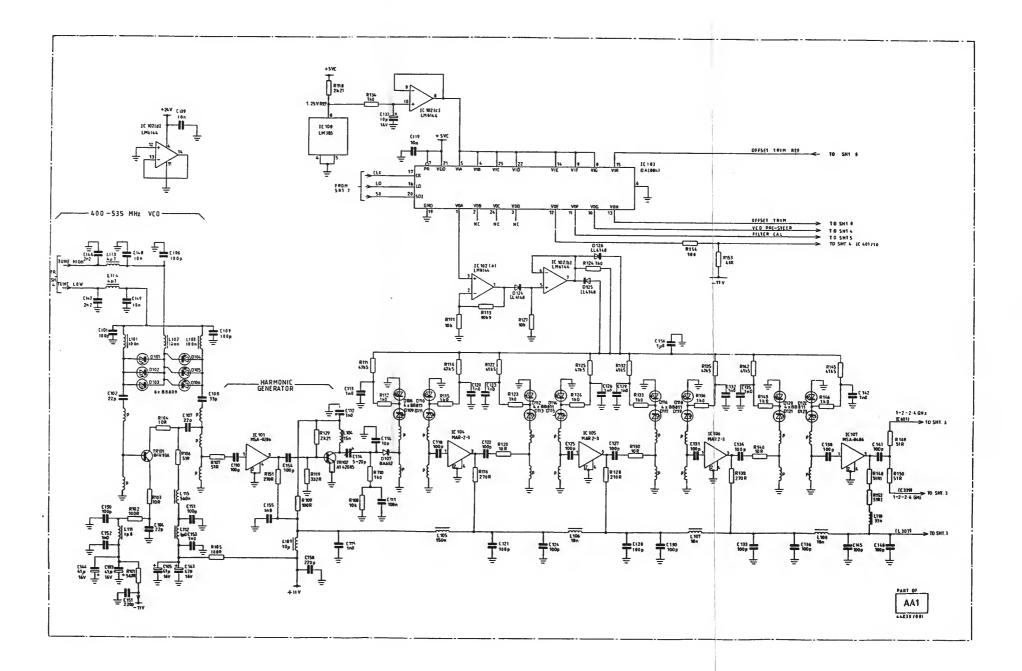

| Carrier frequency synthesis                            | 1-8     |

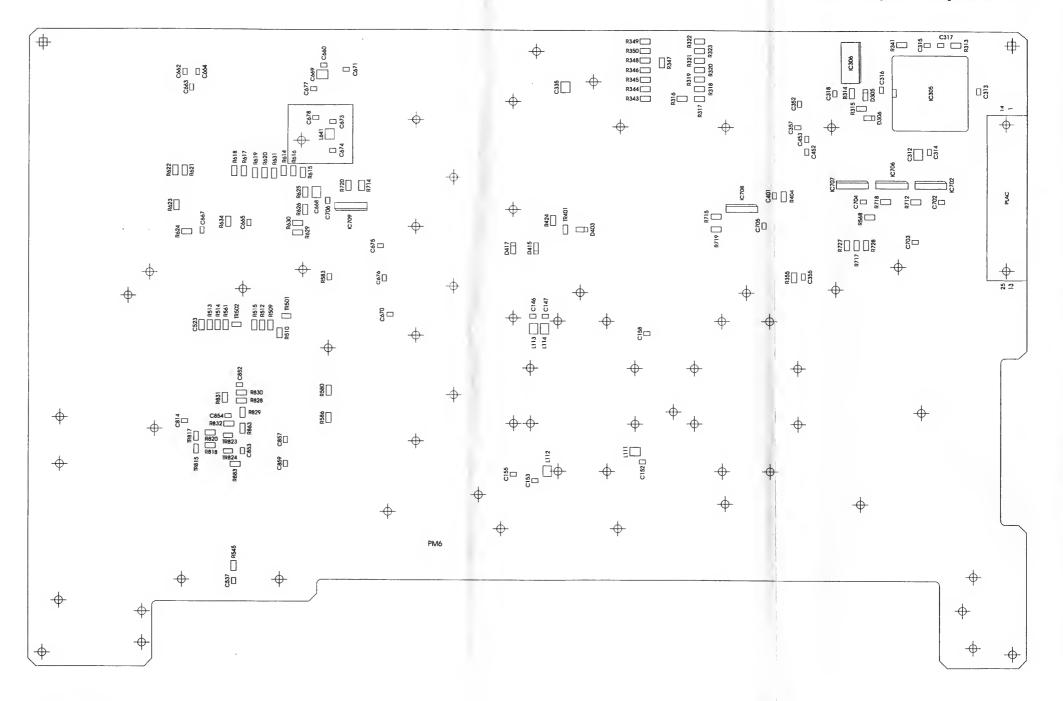

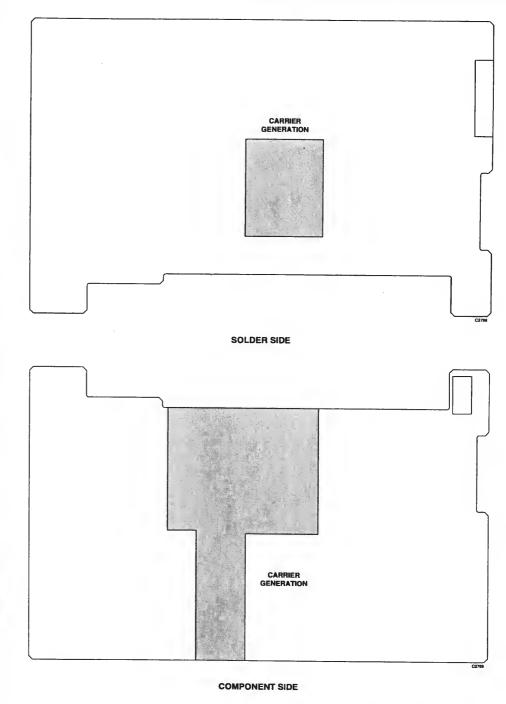

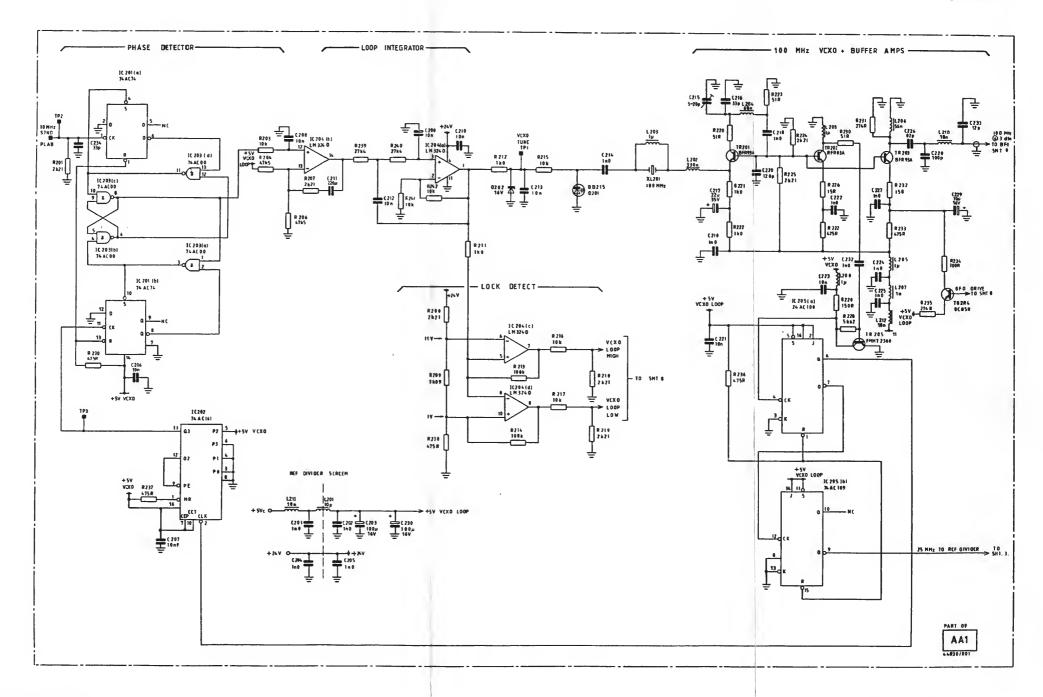

| RF board: Carrier generation (AA1 sheet 1)             | 1-8     |

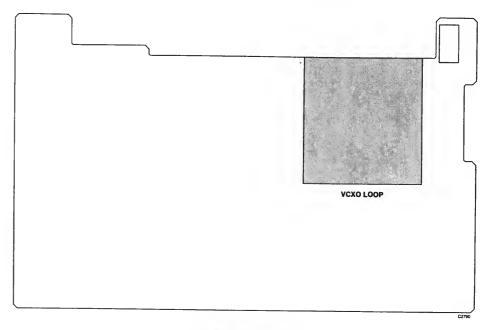

| RF board: VCXO loop (AA1 sheet 2)                      | 1-9     |

| 100 MHz VCX0                                           | 1-9     |

| 100 MHz phase locked loop                              | 1-9     |

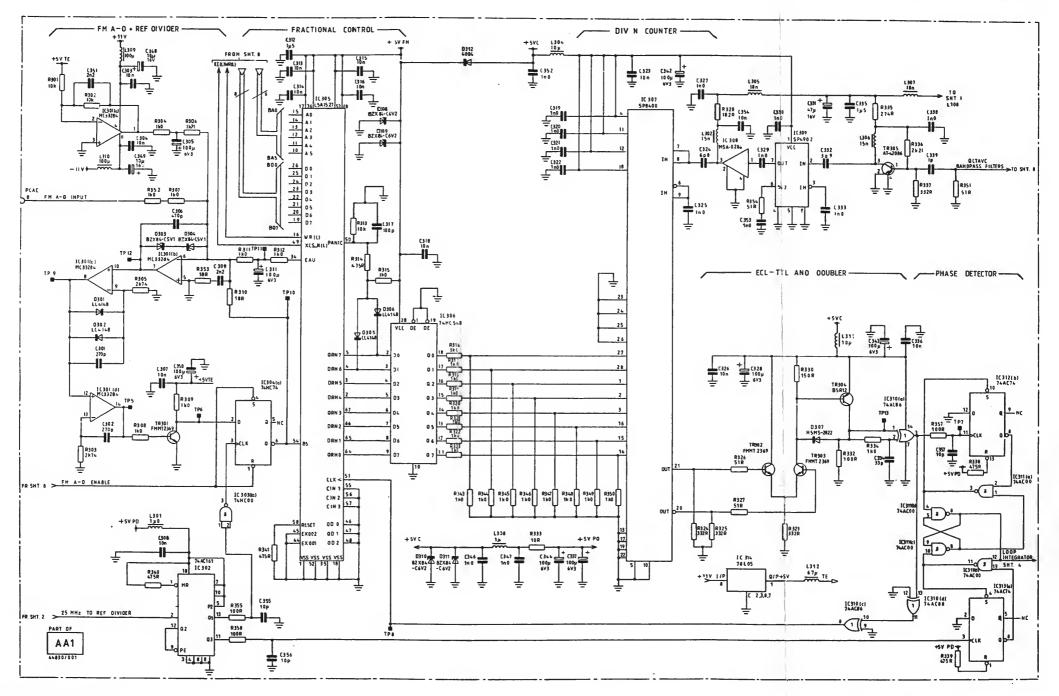

| RF board: Synthesiser (AA1 sheet 3)                    | 1-10    |

| Synthesiser operation                                  | 1-10    |

| 1-bit A-D converter                                    | 1-10    |

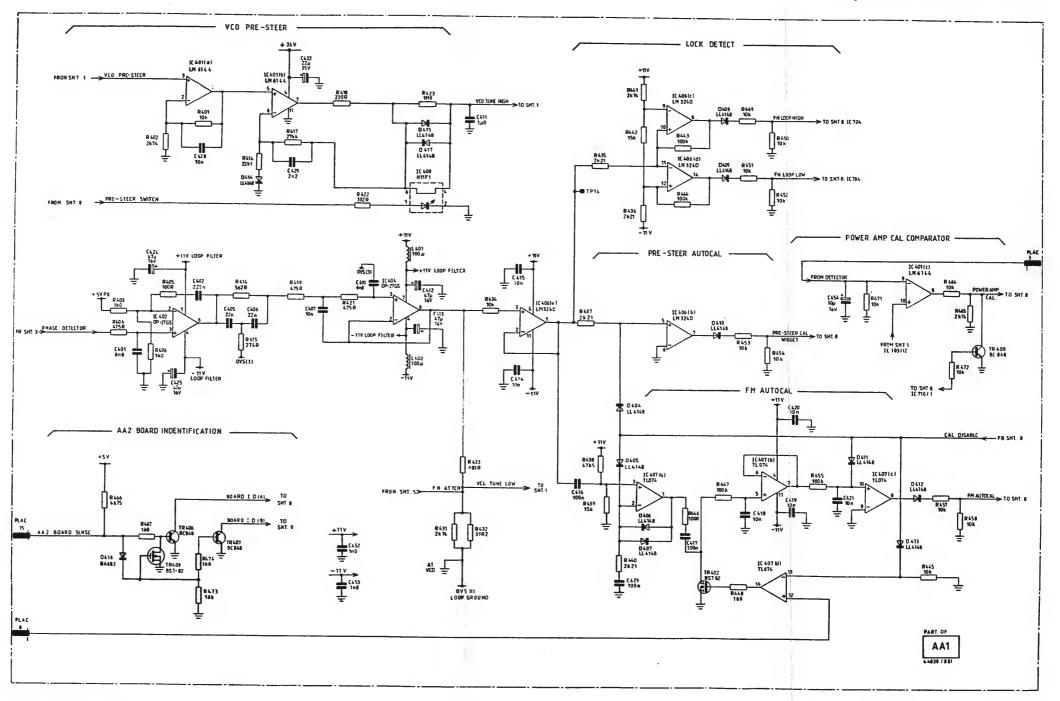

| RF board: Loop filter and autocal (AA1 sheet 4)        | 1-11    |

| Loop filter                                            | 1_11    |

| Autocalibration                                        |         |

| AA2 board identification                               | 1 12    |

| Power amp cal comparator                               | 1 12    |

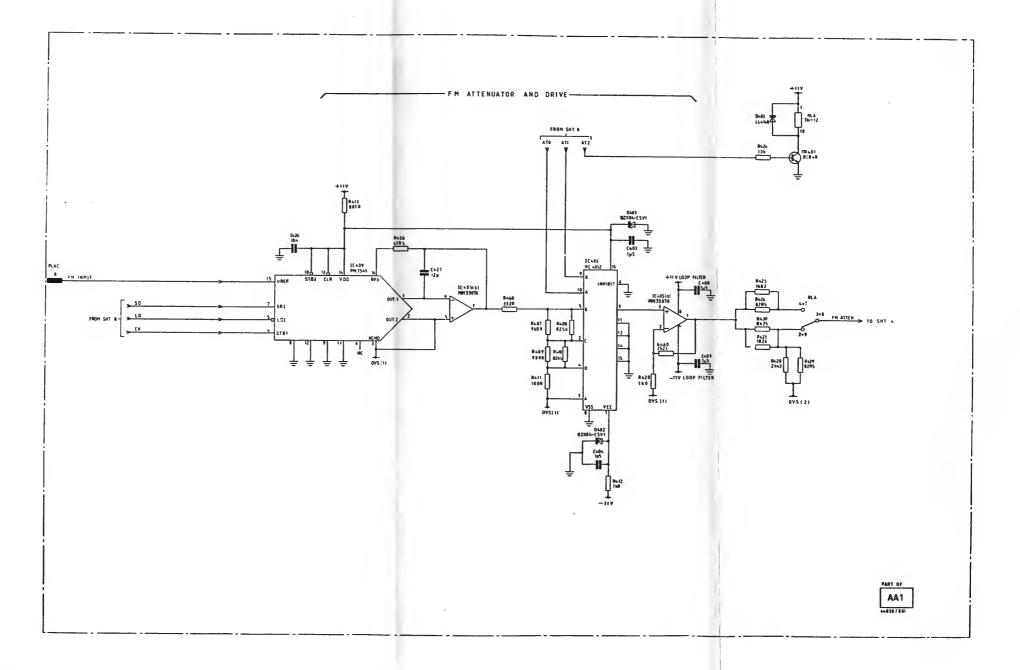

| RF board: FM drive (AA1 sheet 5)                       | 1-13    |

| Operation                                              | 1-13    |

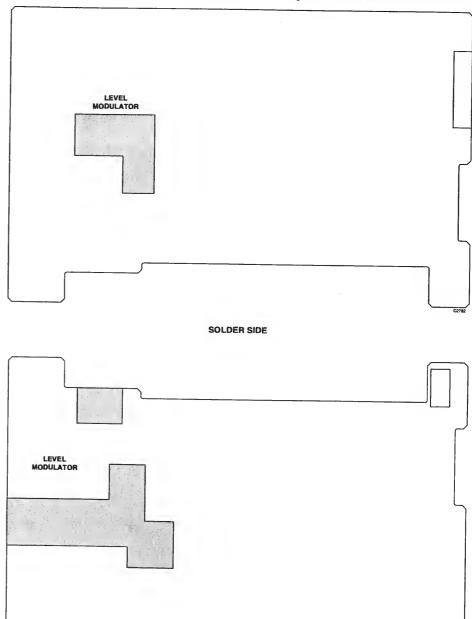

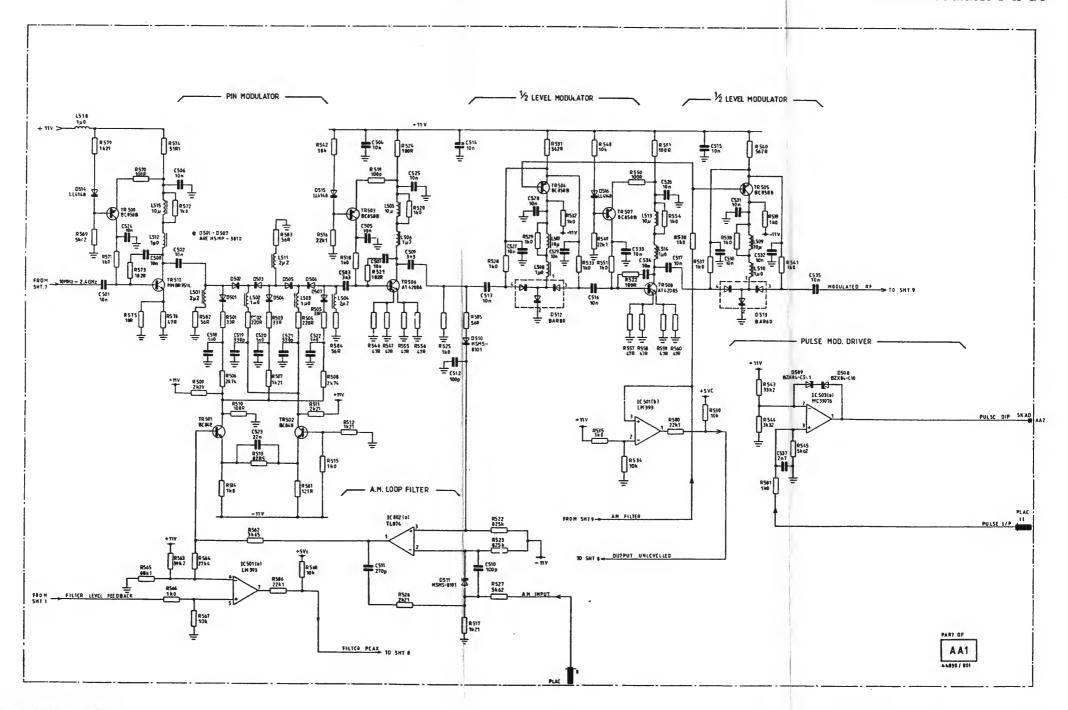

| RF board: Level modulator (AA1 sheet 6)                | 1-13    |

| Amplitude modulator                                    | 1-14    |

| Amplitude modulator                                    | 1-14    |

| PIN modulator                                          | 1-14    |

| Peak detector and control loop                         | 1-15    |

| Level modulator                                        | 1-15    |

| Output unlevelled                                      |         |

| Pulse modulation drive                                 | 1-15    |

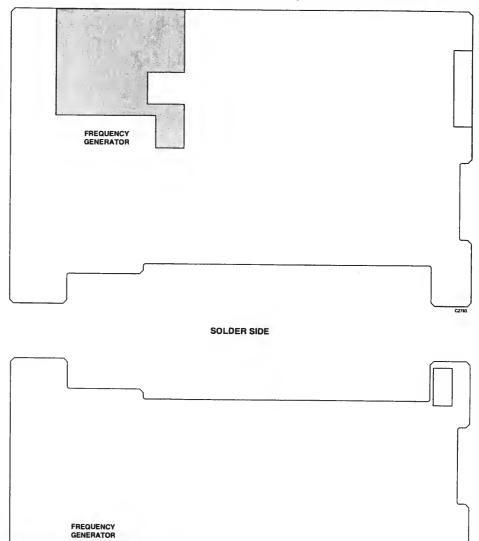

| RF board: Frequency generator (AA1 sheet 7)            | 1-16    |

| Frequency generation                                   | 1-16    |

| Frequency band selection                               | 1-16    |

| Fundamental octave                                     | 1-17    |

| 600 MHz to 1.2 GHz generation                          | 1-17    |

| Programmable divider                                   | 1-17    |

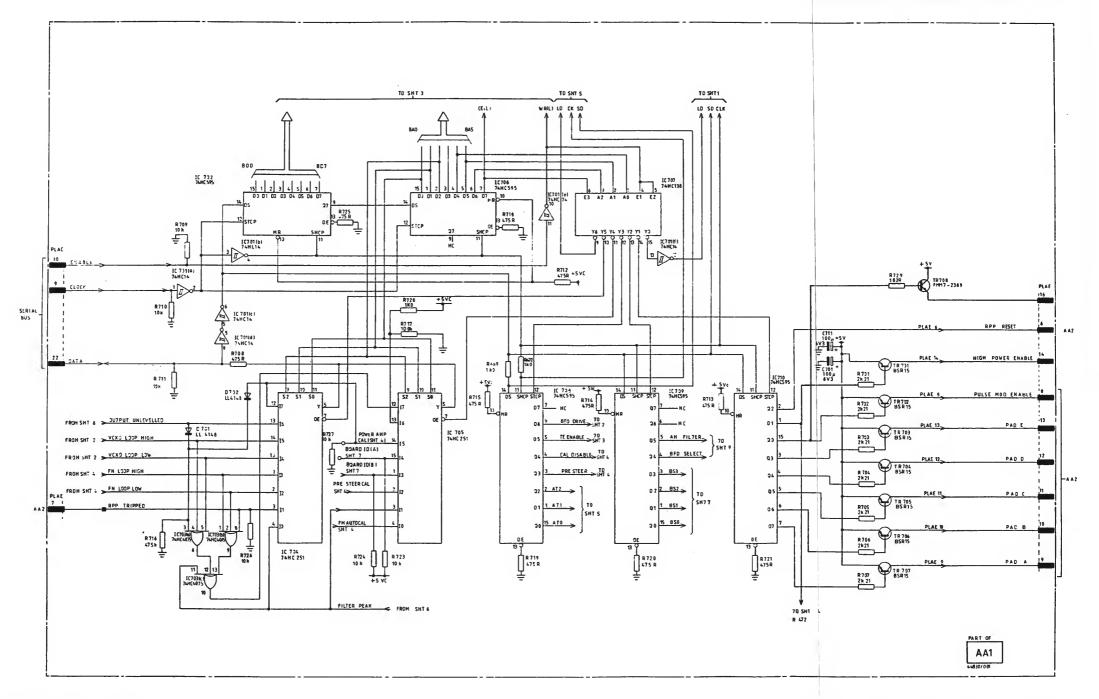

| RF board: Interface and attenuator drive (AA1 sheet 8) | 1-18    |

| Serial bus interface                                   | 1-18    |

| Attenuator drive                                       | 1-18    |

| Pulse modulation                                       | 1-19    |

| RPP control                                            | 1-19    |

| High power amplifier option                            | 1-19    |

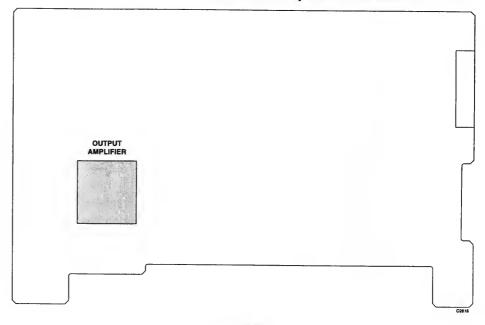

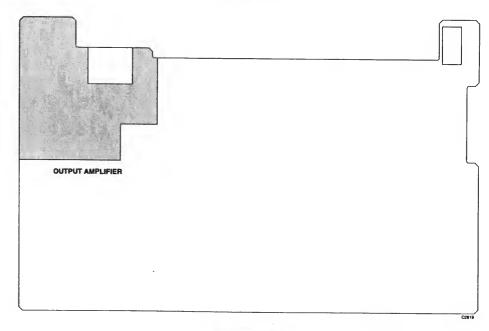

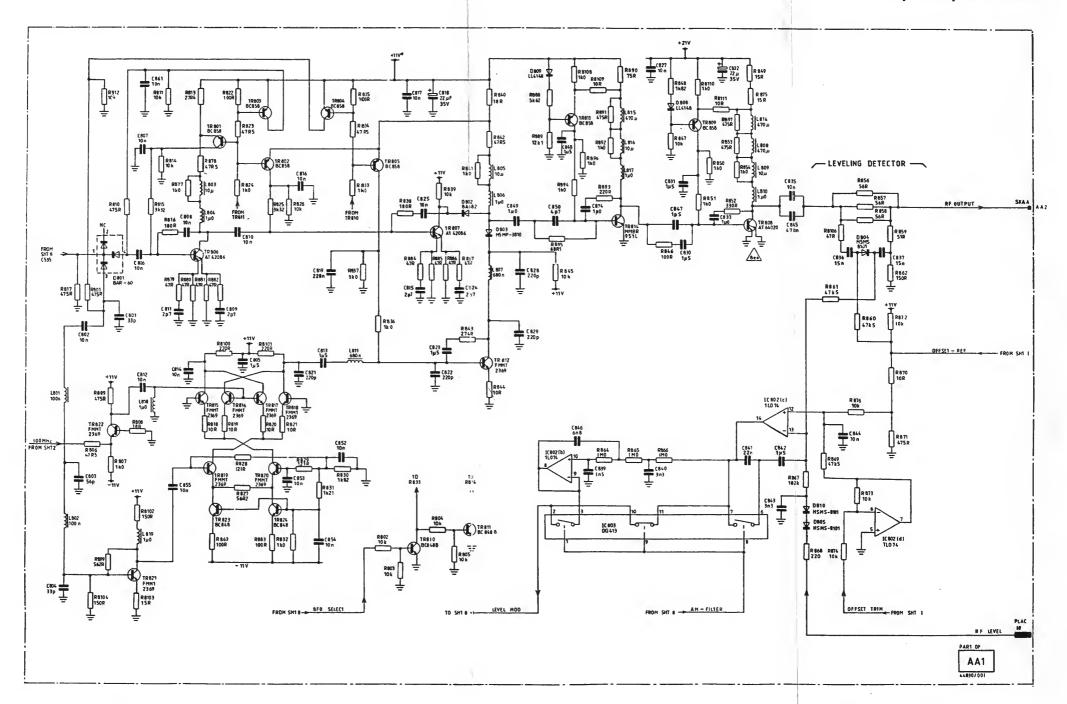

| RF board: output amplifier (AA1 sheet 9)               | 1-19    |

| Output amplifier                                       | 1-19    |

| BFO-band frequency generation                          | 1-19    |

| RF levelling detector                                  | 1-20    |

| ALC loop                                               | 1-20    |

| Offset trim                                            | 1-20    |

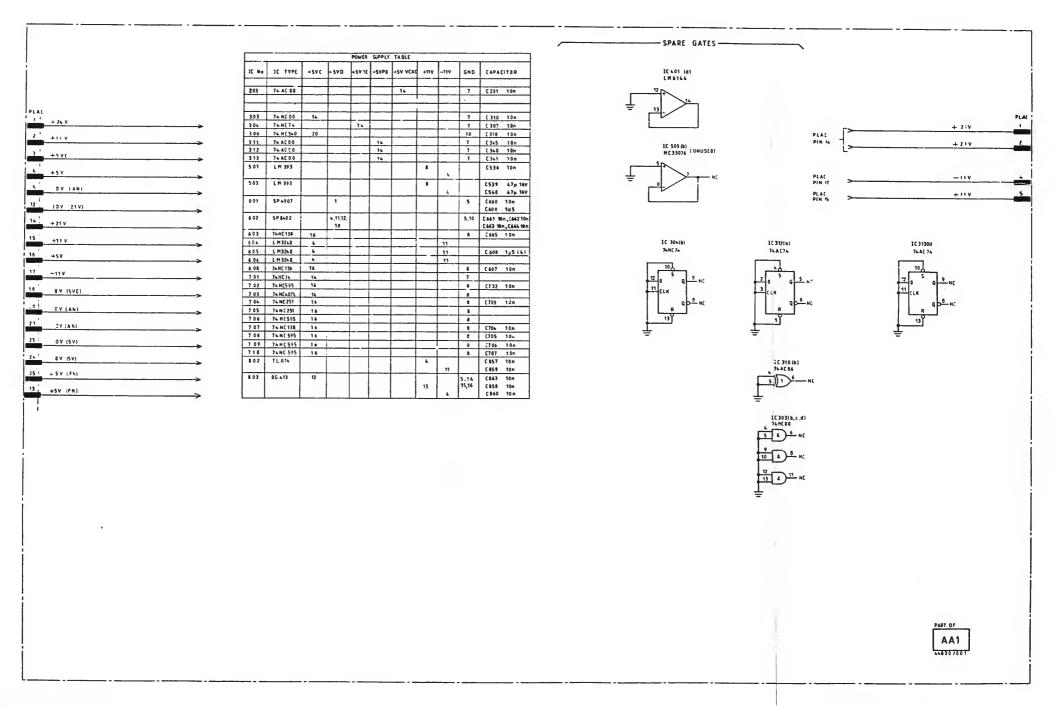

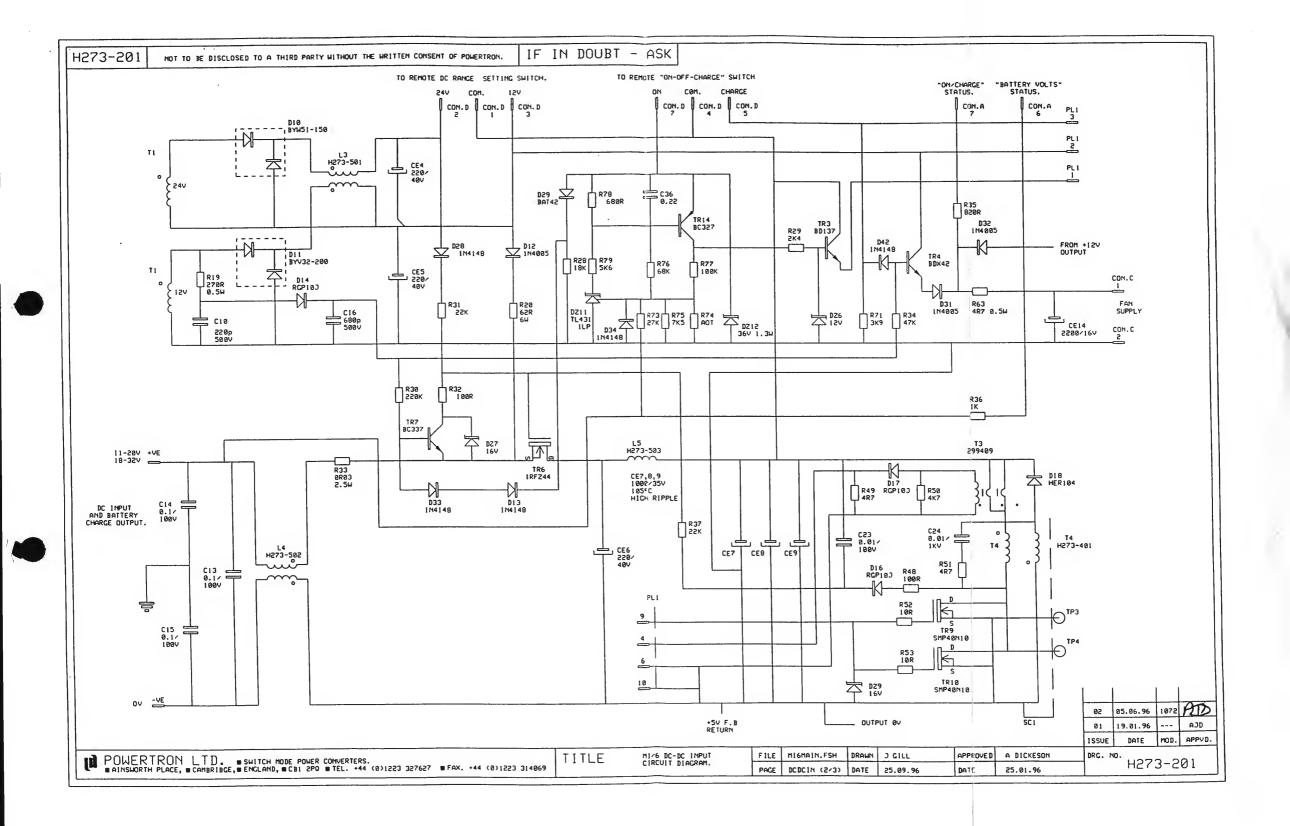

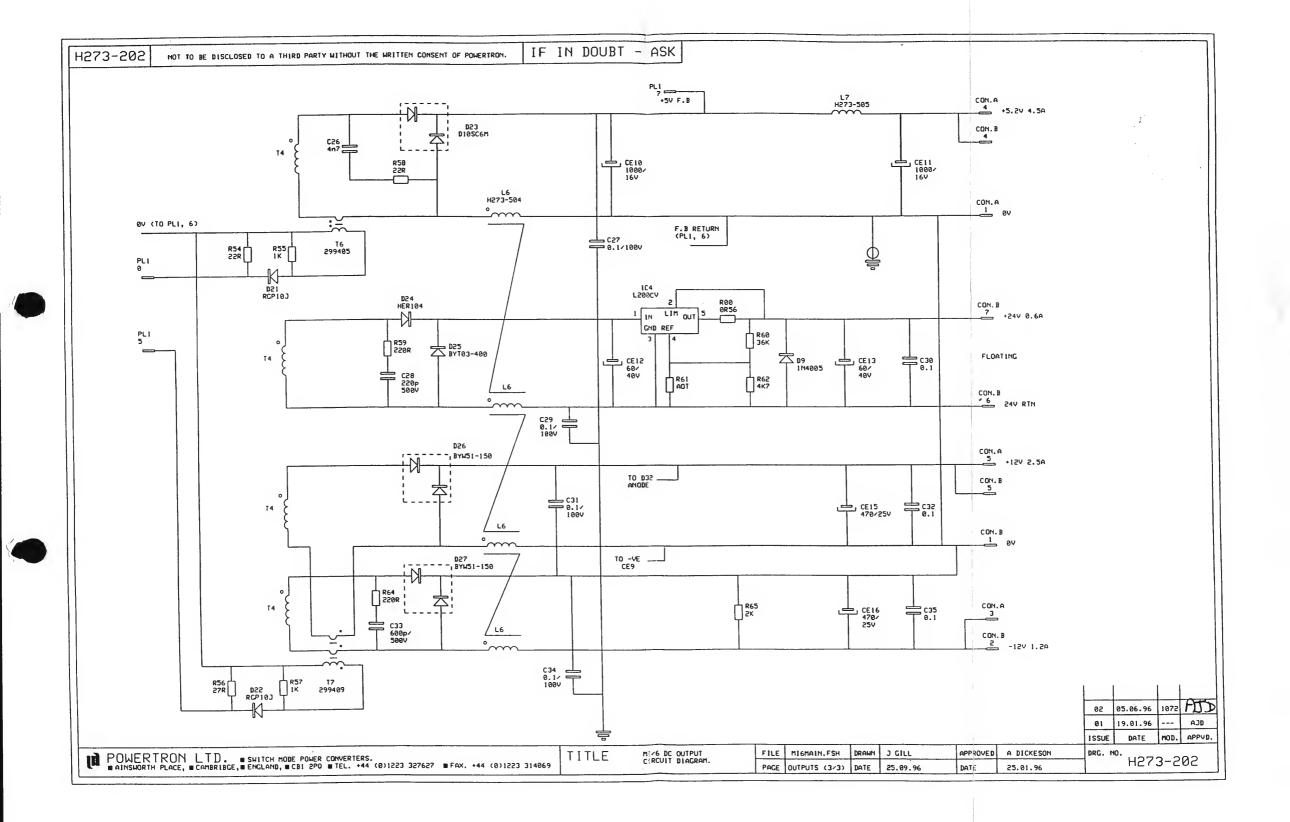

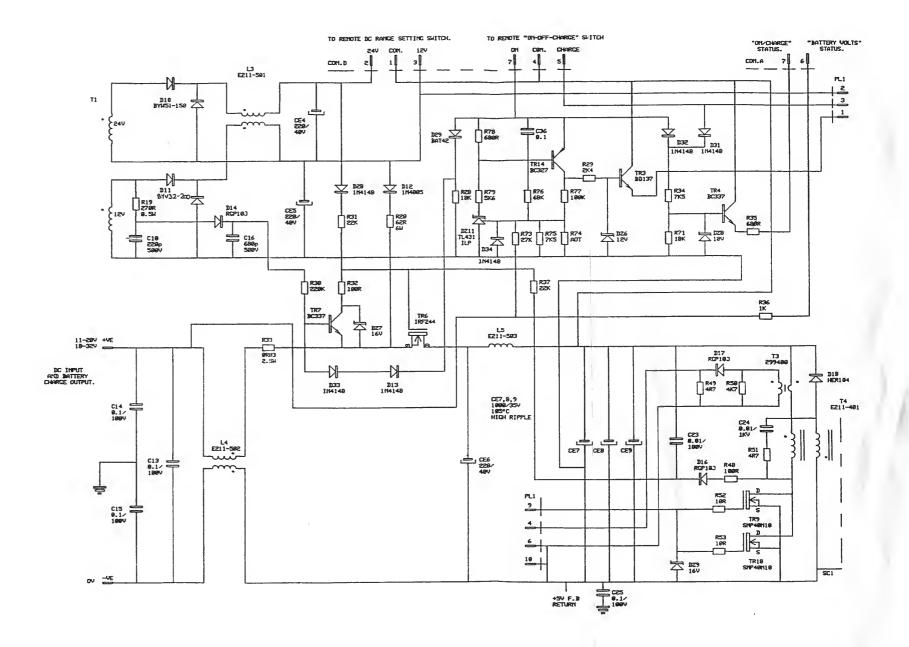

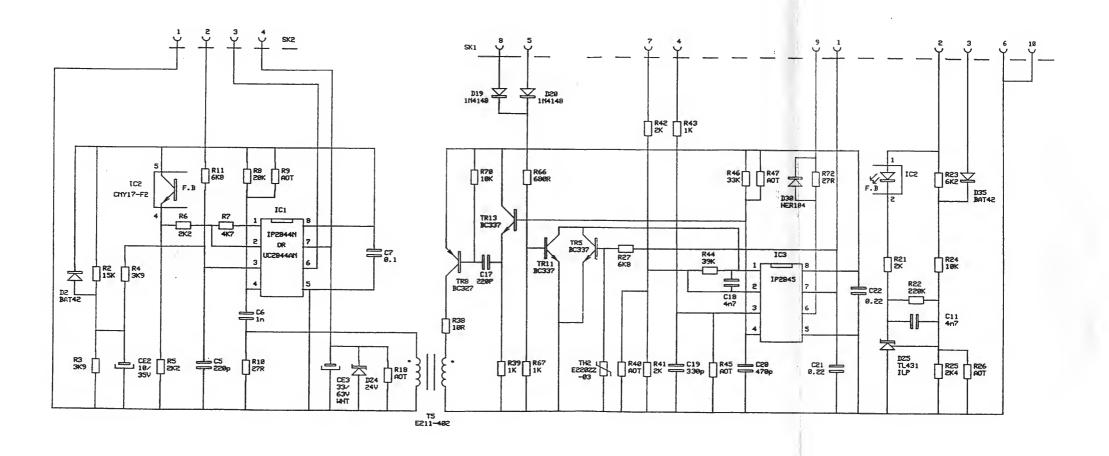

| RF board: Power supplies (AA1 sheet 10)                | 1-20    |

| Power supplies                                         | 1-20    |

|                                                        | contd / |

### **TECHNICAL DESCRIPTION**

### Contents (continued)

| inuea)                                                              |      |

|---------------------------------------------------------------------|------|

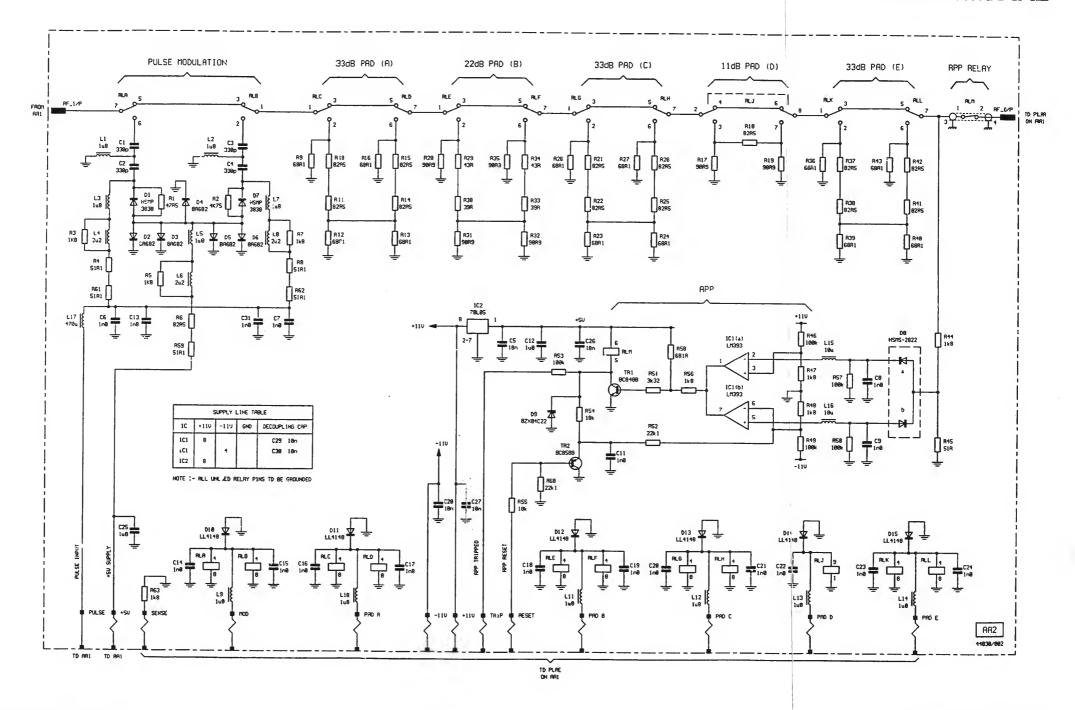

| Attenuator board - AA2                                              |      |

| Circuit functions                                                   | 1-20 |

| Pulse modulation                                                    |      |

| Attenuator                                                          | 1-21 |

| Reverse power protection                                            | 1-21 |

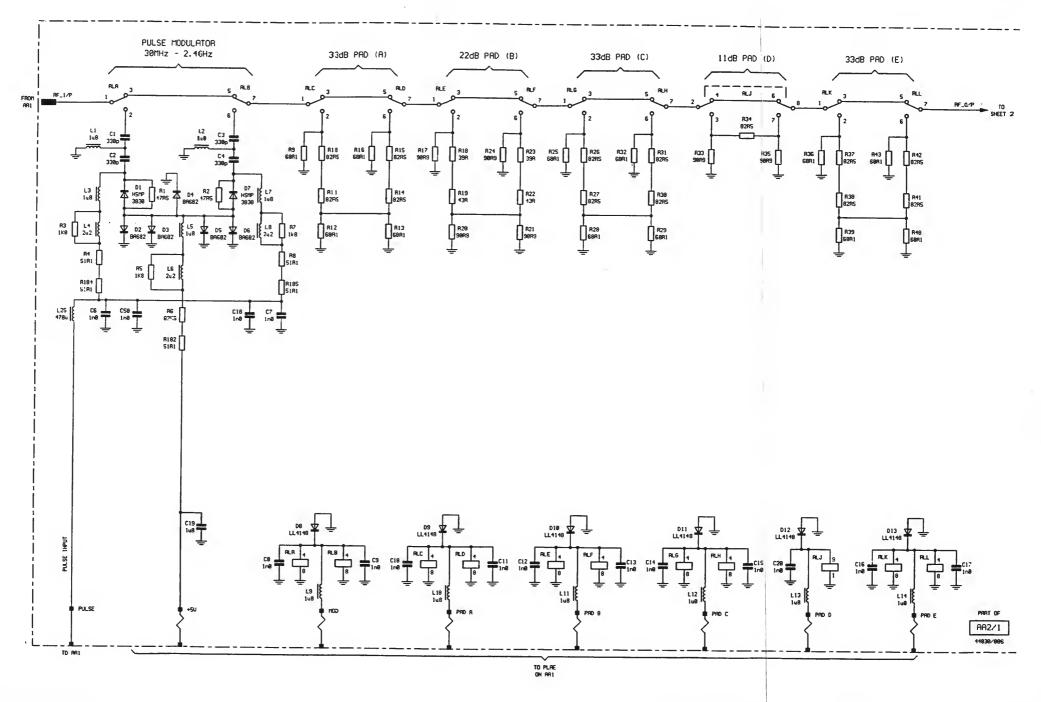

| High power attenuator board - AA2/1                                 | 1-22 |

| Circuit functions                                                   | 1-22 |

| High power attenuator board: Pulse mod & attenuator (AA2/1 sheet 1) | 1-22 |

| Pulse modulation                                                    | 1-22 |

| Attenuator                                                          | 1-22 |

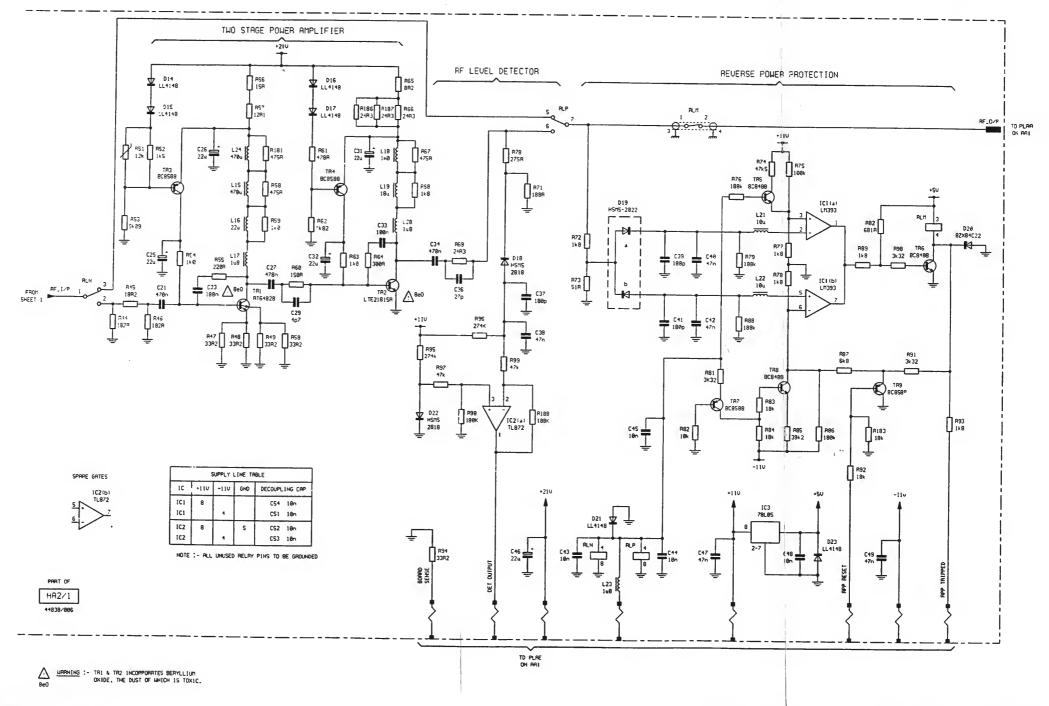

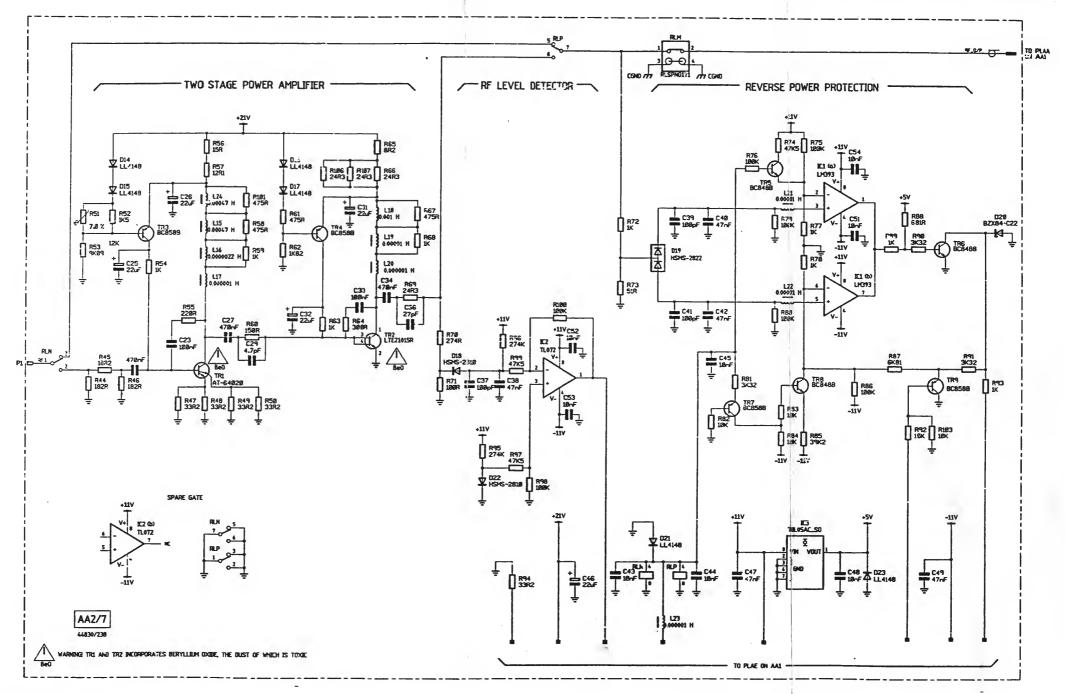

| High power attenuator board: Power amp & RPP (AA2/1 sheet 2)        |      |

| Power amplifier                                                     | 1-23 |

| Reverse power protection                                            | 1-23 |

|                                                                     |      |

| Circuit function                                                    | 1-24 |

| Circuit functions                                                   |      |

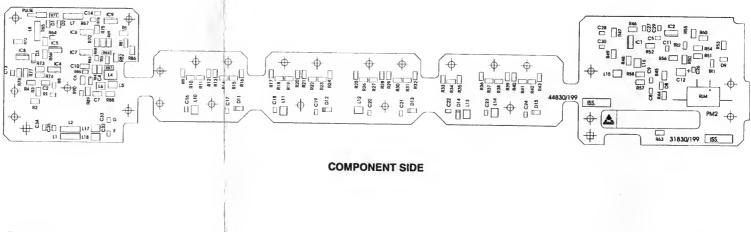

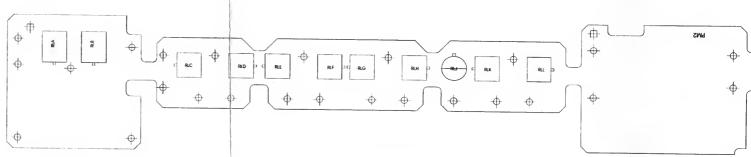

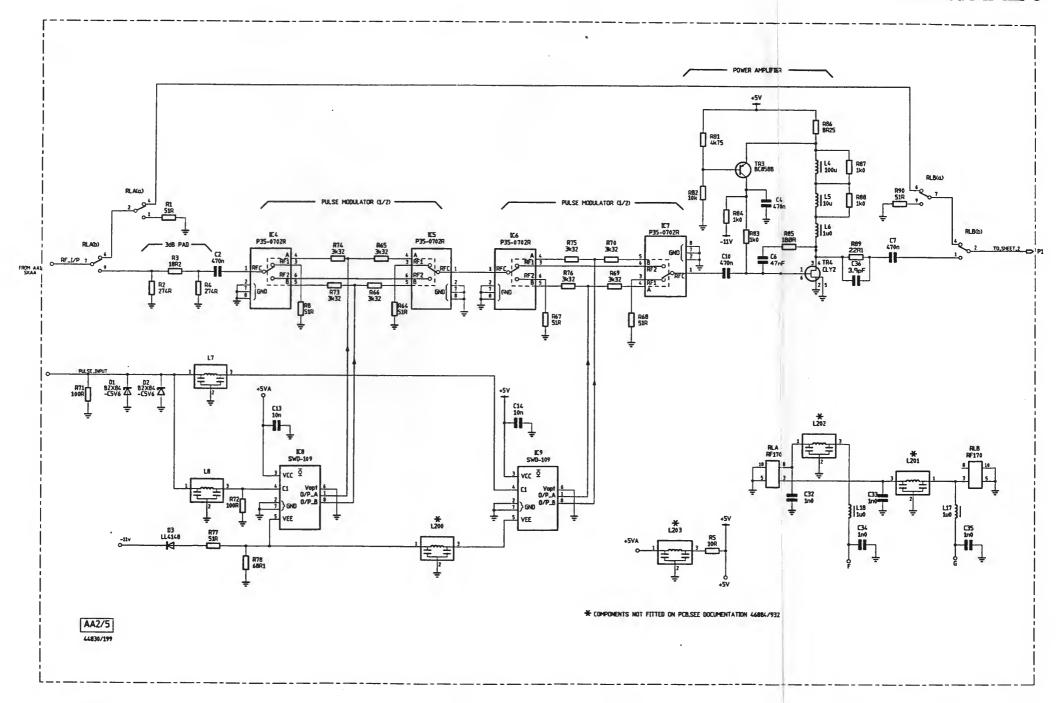

| Fast pulse modulator board: Pulse mod (AA2/5 sheet 1)               | 1-24 |

| Pulse modulation                                                    | 1-24 |

| Amplifier                                                           | 1-24 |

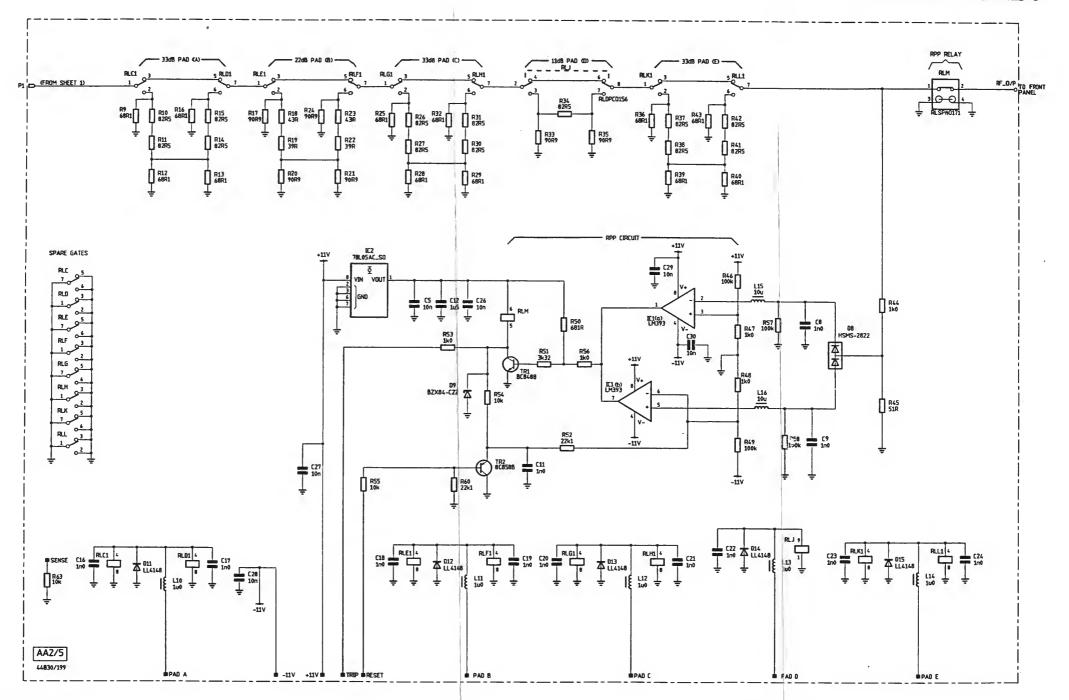

| Fast pulse modulator board: RPP and atten (AA2/5 sheet 2)           | 1-25 |

| Step attenuator                                                     |      |

| Reverse power protection                                            | 1-25 |

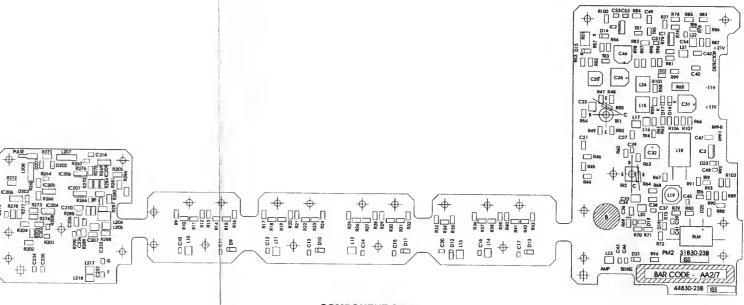

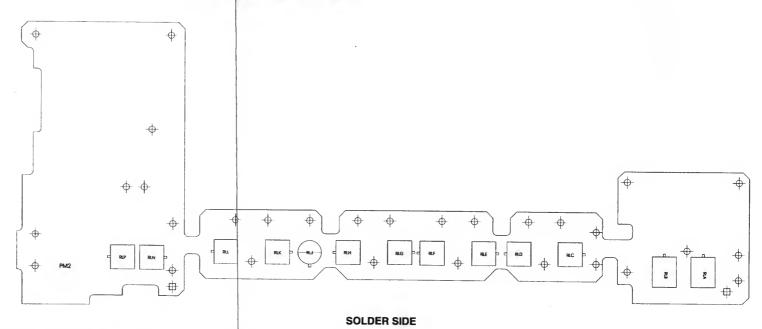

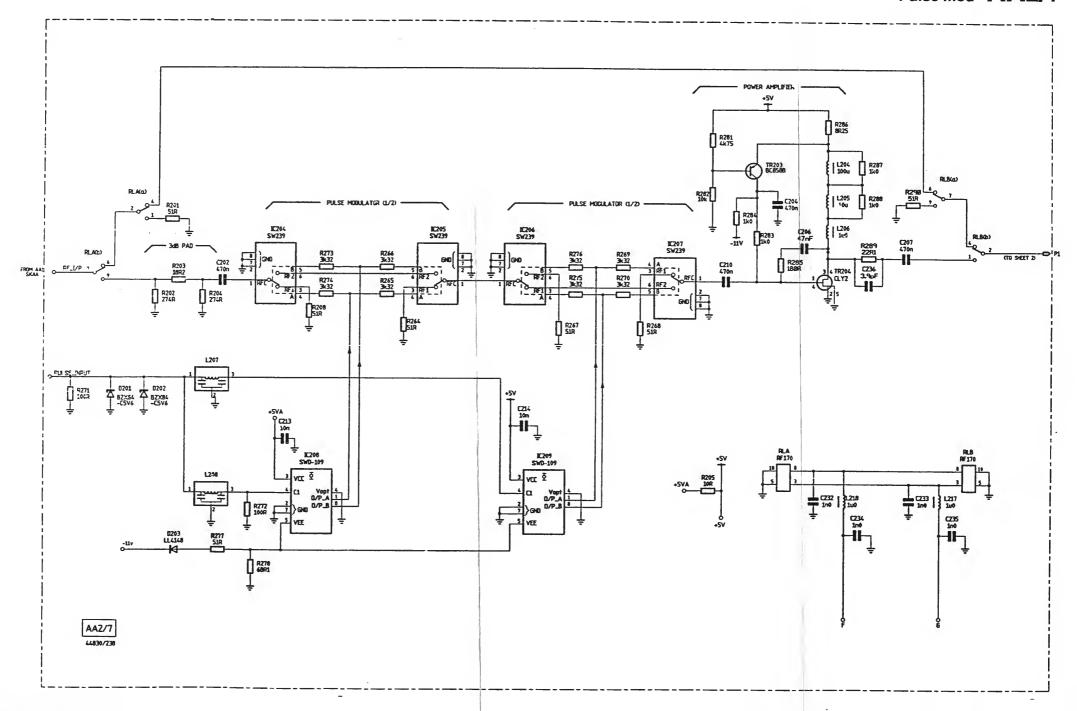

| Fast pulse and high power board - AA2/7                             | 1-23 |

| Circuit functions                                                   |      |

| Fast pulse and high power board: Pulse mod (AA2/7 sheet 2)          | 1-20 |

| Pulse modulation.                                                   | 1-20 |

| Amplifier                                                           | 1-20 |

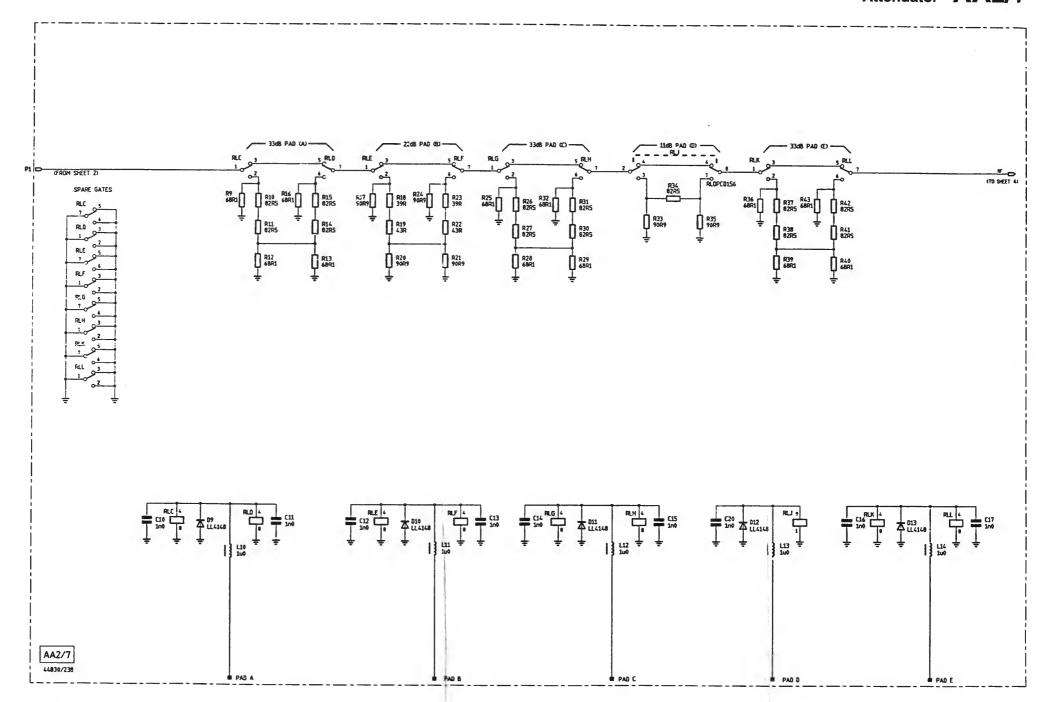

| Fast pulse and high power board: Attenuator (AA2/7 sheet 3).        | 1-20 |

| Attenuator                                                          |      |

| Fast pulse and high power board: Power amp & RPP (AA2/7 sheet 4)    | 1-27 |

| Power amplifier                                                     | 1-27 |

| Reverse power protection                                            | 1-27 |

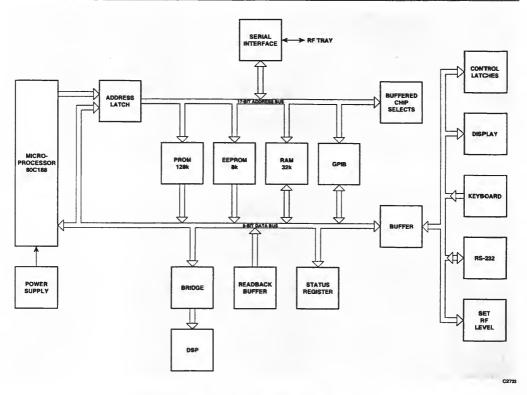

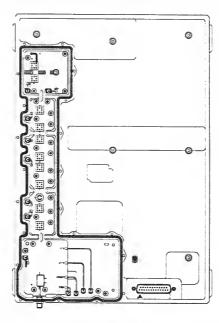

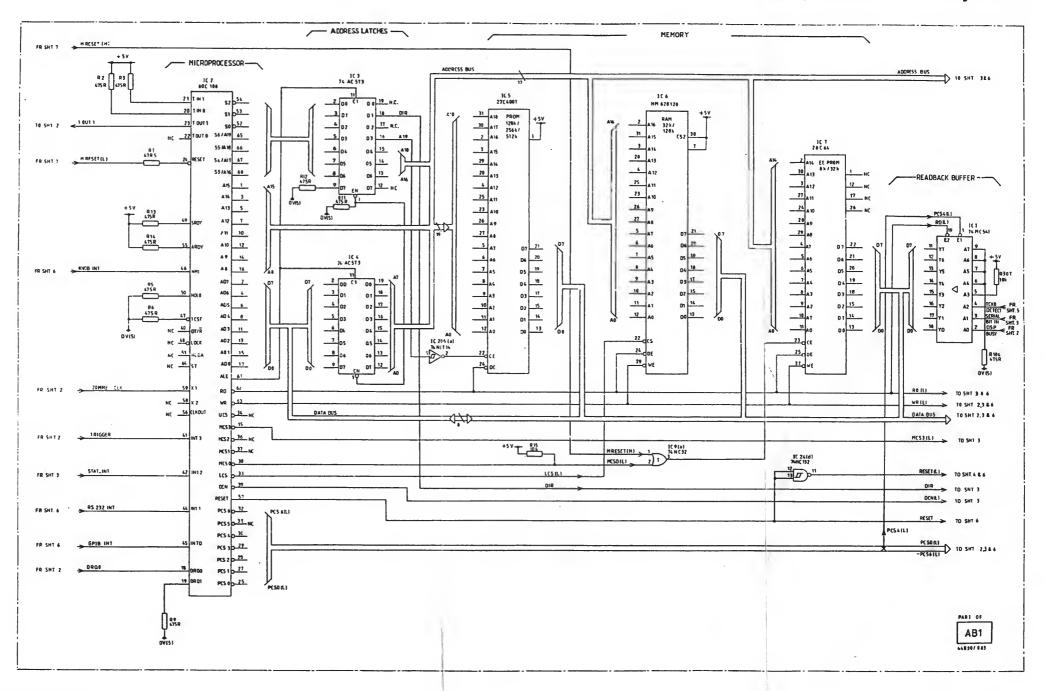

| Control board - AB1                                                 | 1-28 |

| Introduction                                                        | 1-28 |

| Control board: Microprocessor and memory (AB1 sheet 1)              | 1-28 |

| Microprocessor                                                      |      |

| Interrupts                                                          |      |

| Memory bank                                                         |      |

| Data transfer                                                       |      |

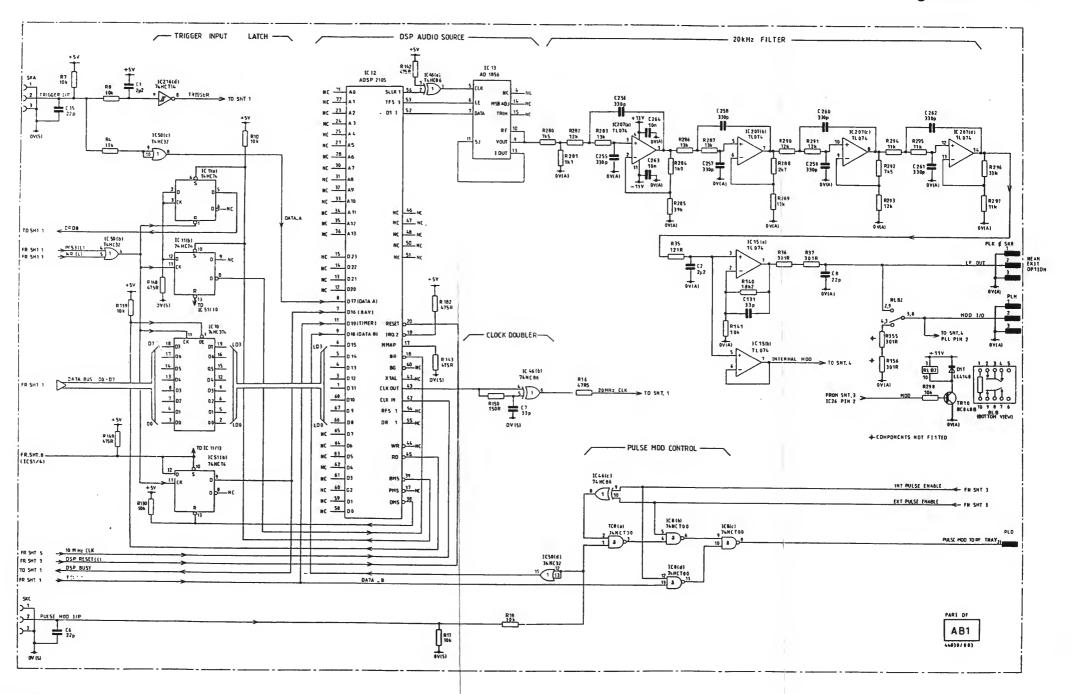

| Control board: DSP audio generator (AB1 sheet 2)                    | 1-31 |

| Trigger                                                             | 1-31 |

| Pulse modulation                                                    | 1-32 |

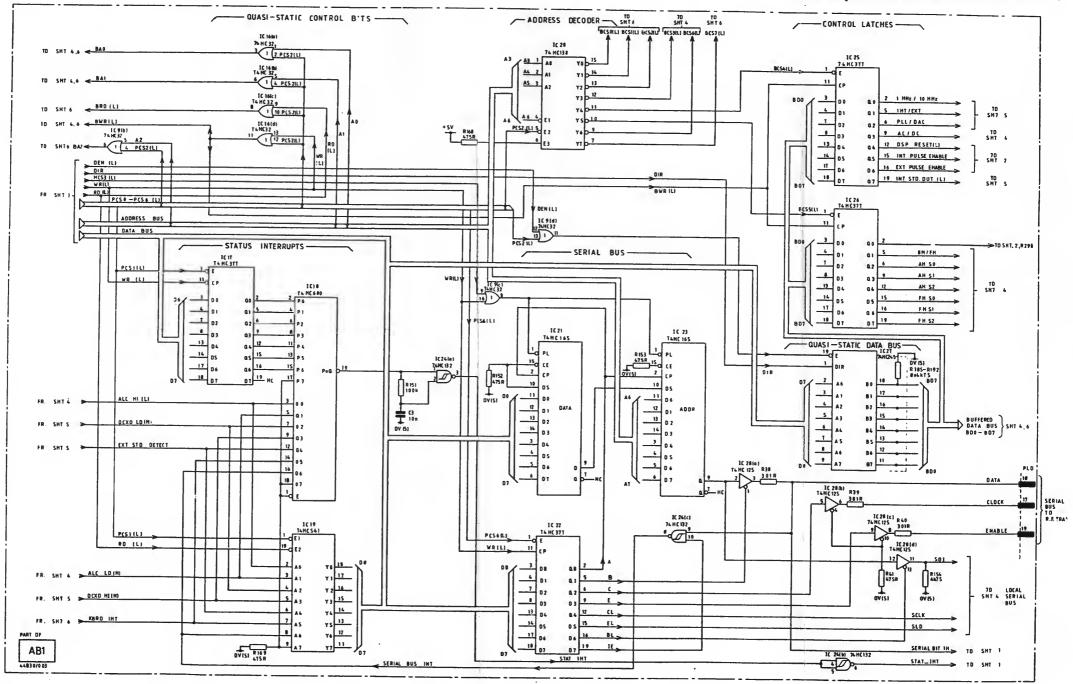

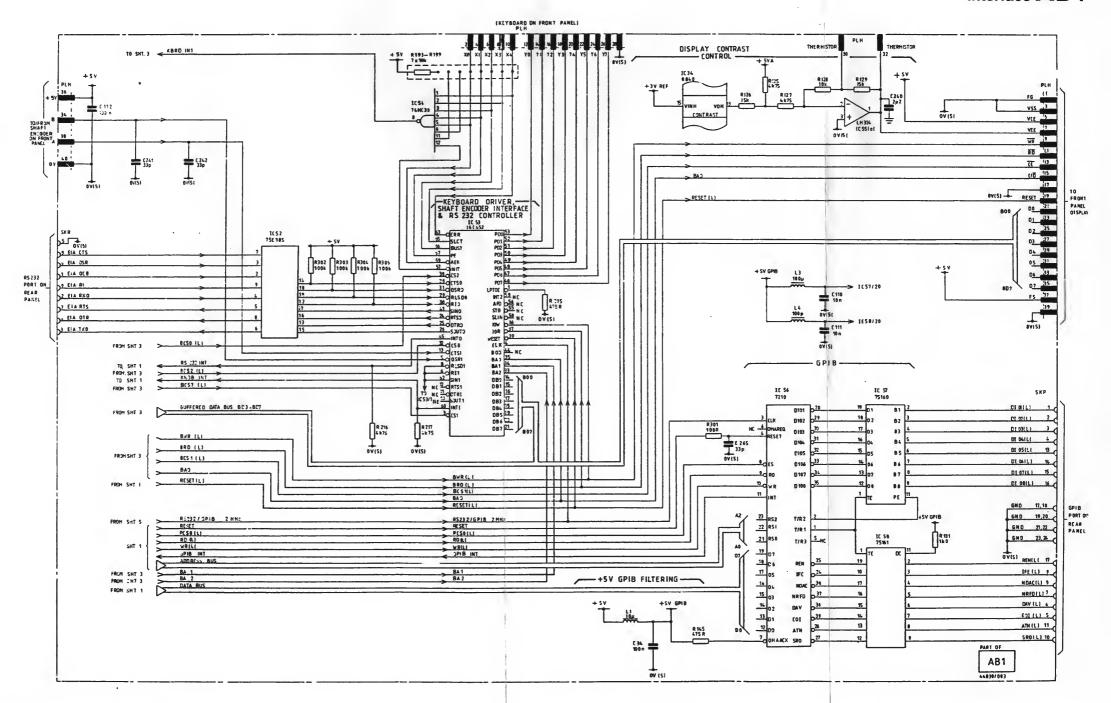

| Control board: Interrupts and serial interface (AB1 sheet 3)        | 1-32 |

| Interrupt handler                                                   | 1-32 |

| Serial bus                                                          | 1-32 |

| Buffered data bus and control lines                                 | 1-33 |

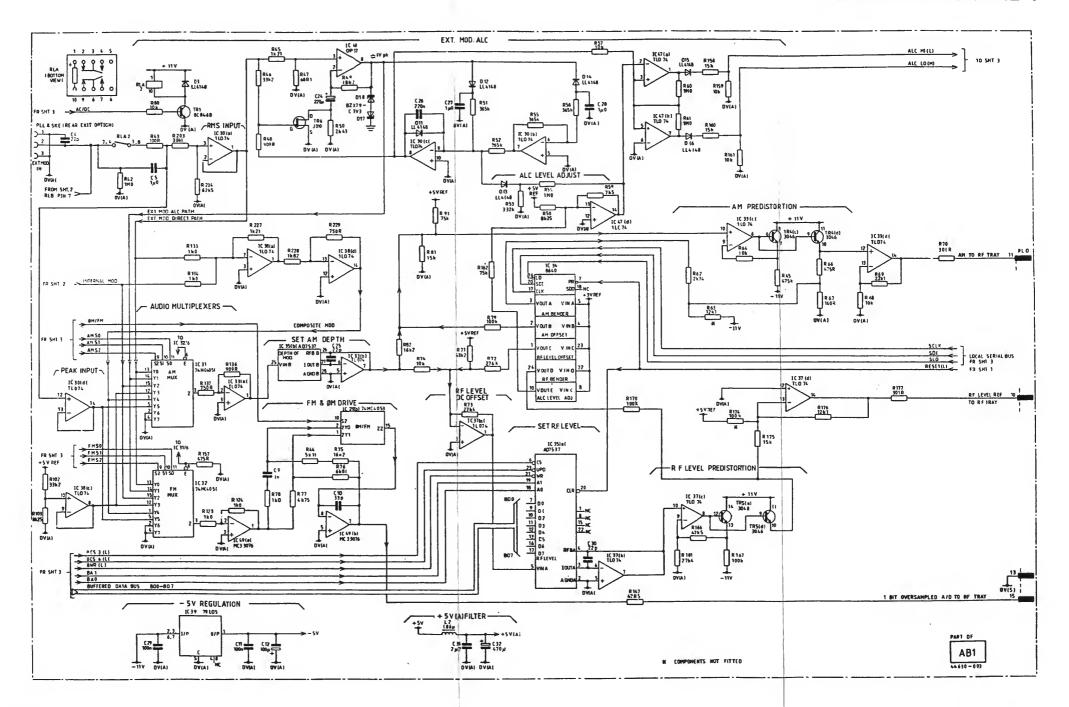

| Control board: Modulation and level (AB1 sheet 4)                   | 1-34 |

| External modulation input                                           | 1-34 |

| Composite modulation                                                | 1-34 |

| Amplitude modulation                                                | 1-34 |

| Frequency/Phase modulation                                          | 1-34 |

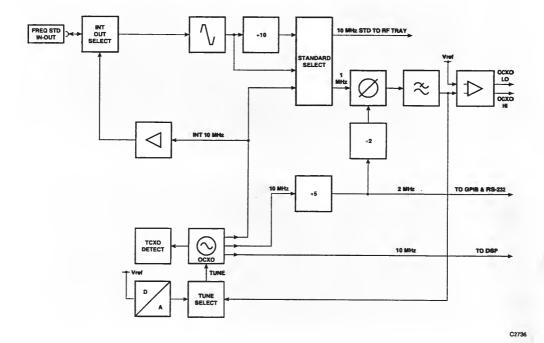

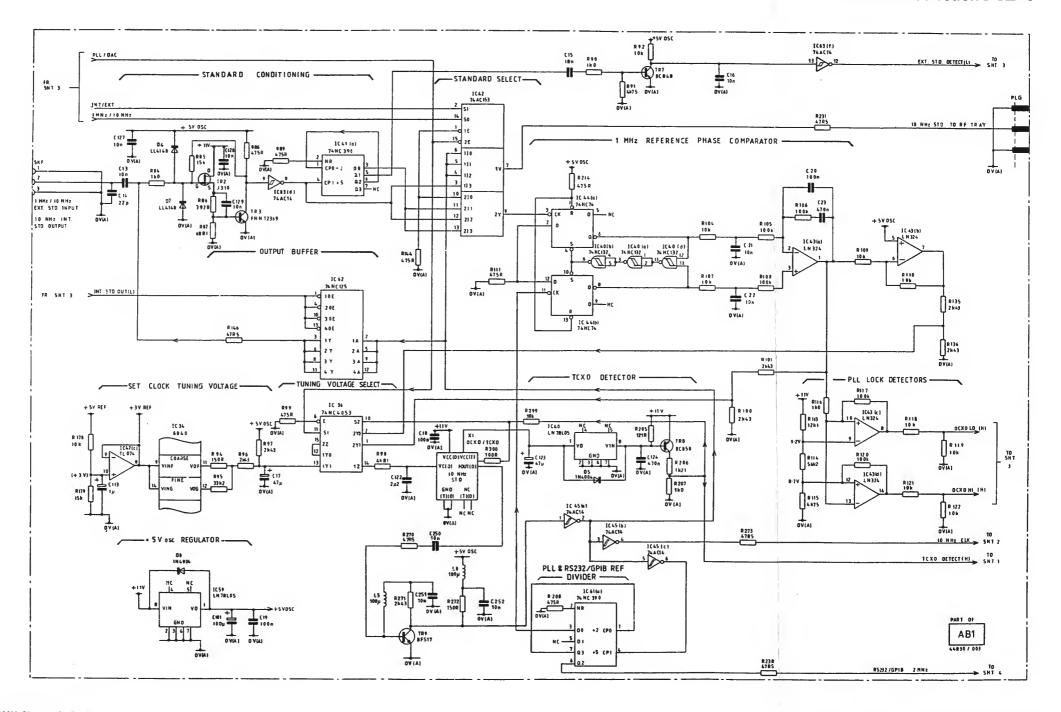

| Control board: Standard selection (AB1 sheet 5)                     | 1-35 |

| Clock circuitry                                                     | 1-35 |

| Control board: Interface (AB1 sheet 6)                              | 1-36 |

| GPIB                                                                | 1-36 |

| RS-232                                                              | 1-36 |

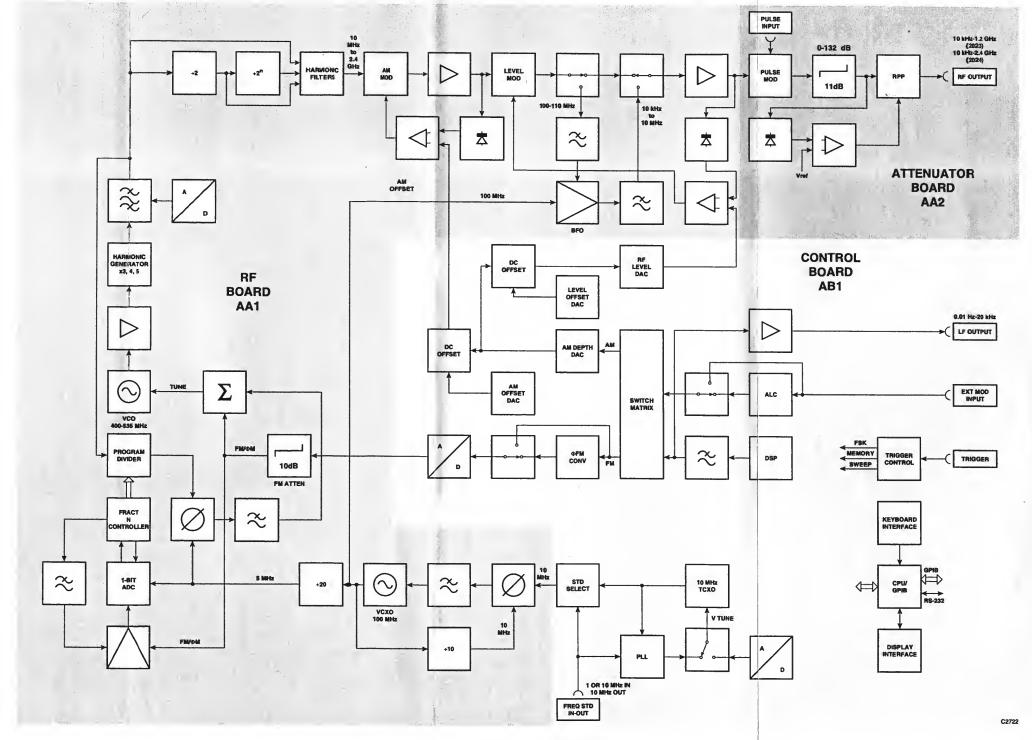

| Fig. 1-1   Signal generator block schematic   1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |                                                |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------|------|

| Front panel display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |                                                |      |

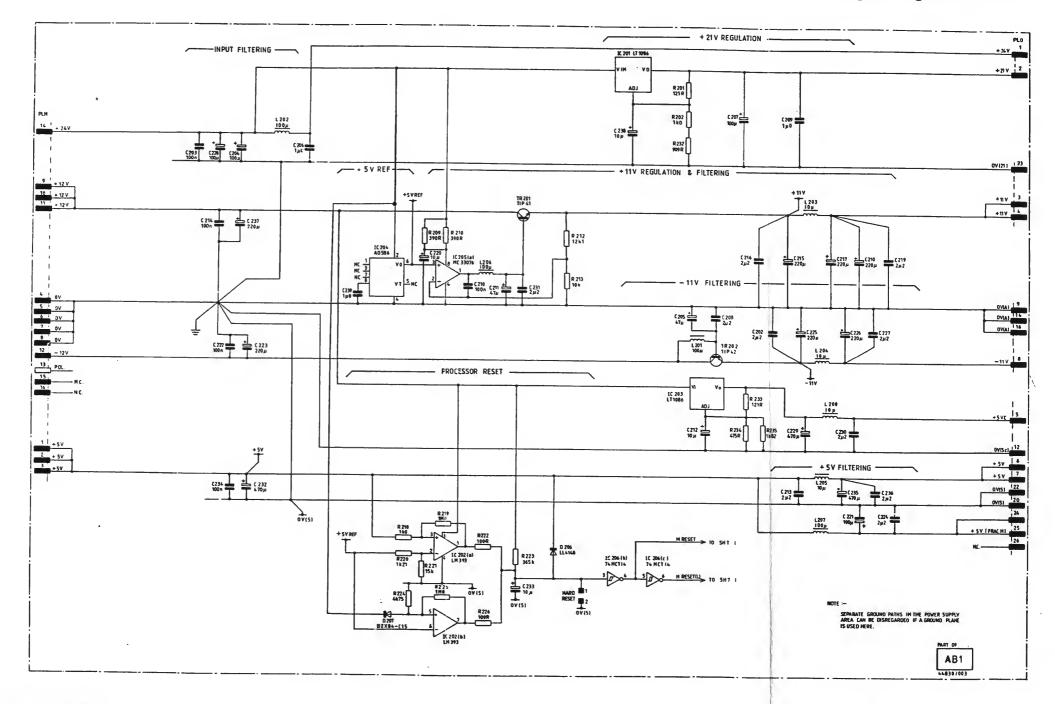

| Control board: PSU filtering and regulation (AB1 sheet 7)   1-37     Processor reset   1-38     Control board: Power supplies (AB1 sheet 8)   1-38     Power supplies   1-38     Power supplies   1-39     Backlight inverter board - AC1   1-39     Front panel - AF1   1-39     AC power supply   1-39     AC power supply   1-39     AC/DC power supply   1-39     List of figures   1-5     Fig. 1-1   Signal generator block schematic   1-5     Fig. 1-2   100 MHz phase locked loop   1-9     Fig. 1-3   Frequency synthesis   1-11     Fig. 1-4   FM/\pM drive   1-14     Fig. 1-5   Frequency band selection   1-17     Fig. 1-6   Microprocessor and control block diagram   1-29     Fig. 1-7   Frequency standard selection   1-36     Fig. 1-8   Block diagram of AC/DC power supply module   1-40     List of tables   1-12   Attenuator board identification   1-12     Table 1-3:   Attenuator board identification   1-16     Table 1-5:   Attenuator selection   1-16     Table 1-6:   Interrupts and chip selects   1-30     Table 1-7:   Memory bank addressing   1-30     Table 1-9:   Latch control lines   1-32     Table 1-10:   Buffered chip selects   1-33     Table 1-10:   Buffered chip selects   1-34                                                                                                                                                      |                 |                                                |      |

| Processor reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Front panel     | displaydisplay                                 | 1-37 |

| Control board: Power supplies (AB1 sheet 8)   1-38     Power supplies   1-38     Backlight inverter board - AC1   1-39     Front panel - AF1   1-39     AC power supply   1-39     AC power supply   1-39     AC/DC power supply   1-39     List of figures   1-1     Fig. 1-2   100 MHz phase locked loop   1-9     Fig. 1-3   Frequency synthesis   1-11     Fig. 1-4   FM/φM drive   1-14     Fig. 1-5   Frequency band selection   1-17     Fig. 1-6   Microprocessor and control block diagram   1-29     Fig. 1-7   Frequency standard selection   1-36     Fig. 1-8   Block diagram of AC/DC power supply module   1-40     List of tables   1-1:   Carrier generation   1-12     Table 1-3:   Attenuator board identification   1-12     Table 1-4:   Frequency band selection   1-16     Table 1-5:   Attenuator control settings   1-13     Table 1-6:   Interrupts and chip selectis   1-30     Table 1-7:   Memory bank addressing   1-30     Table 1-8:   Interrupt lines   1-33     Table 1-9:   Latch control lines   1-33     Table 1-9:   Latch control lines   1-33     Table 1-10:   Buffered chip selects   1-34     Table | Control boa     | rd: PSU filtering and regulation (AB1 sheet 7) | 1-37 |

| Power supplies   1-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Process         | or reset                                       | 1-38 |

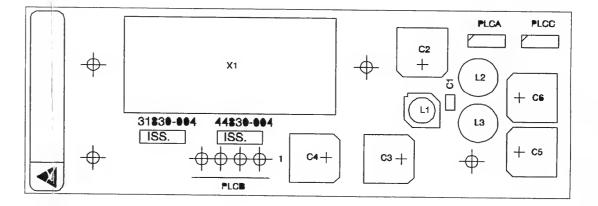

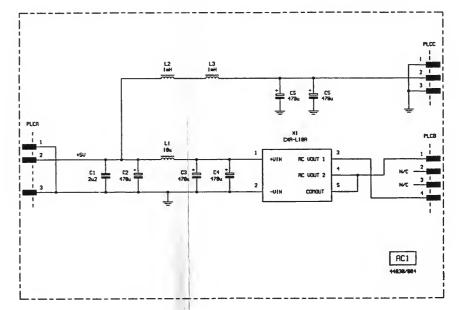

| Backlight inverter board - AC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Control boar    | rd: Power supplies (AB1 sheet 8)               | 1-38 |

| Front panel - AF1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Power s         | supplies                                       | 1-38 |

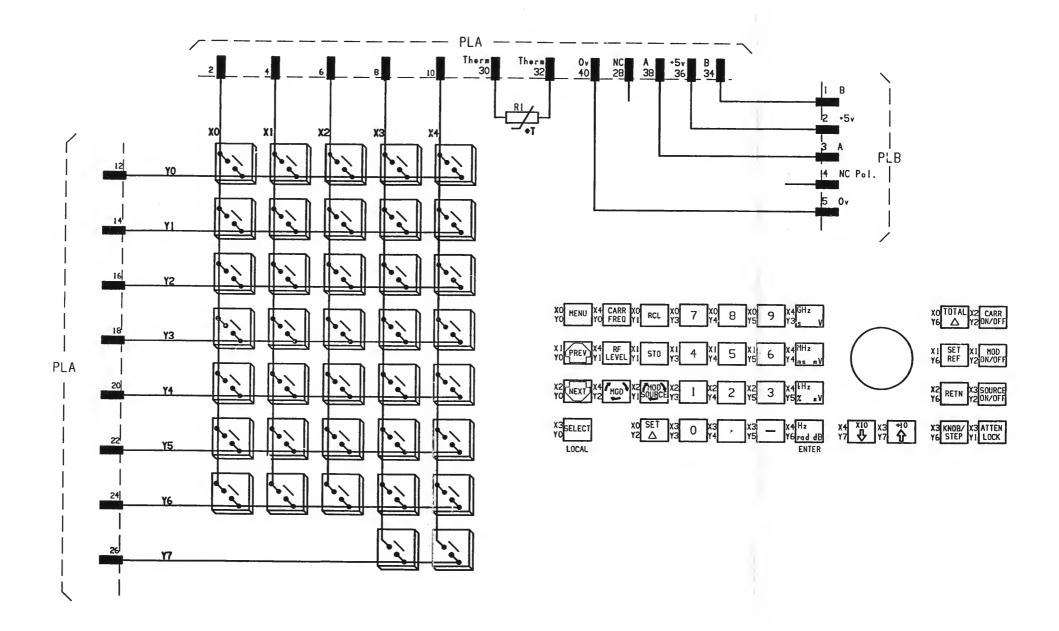

| Front panel - AF1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Backlight in    | verter board - AC1                             | 1-39 |

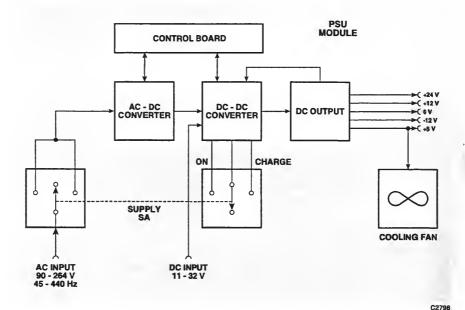

| AC power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Front panel     | - AF1                                          | 1-39 |

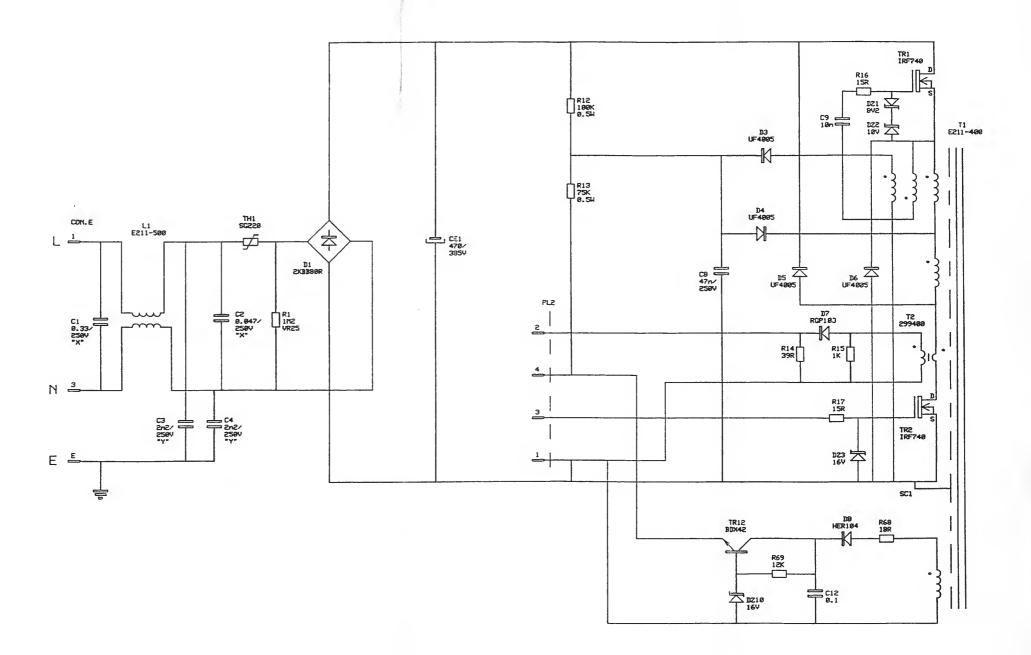

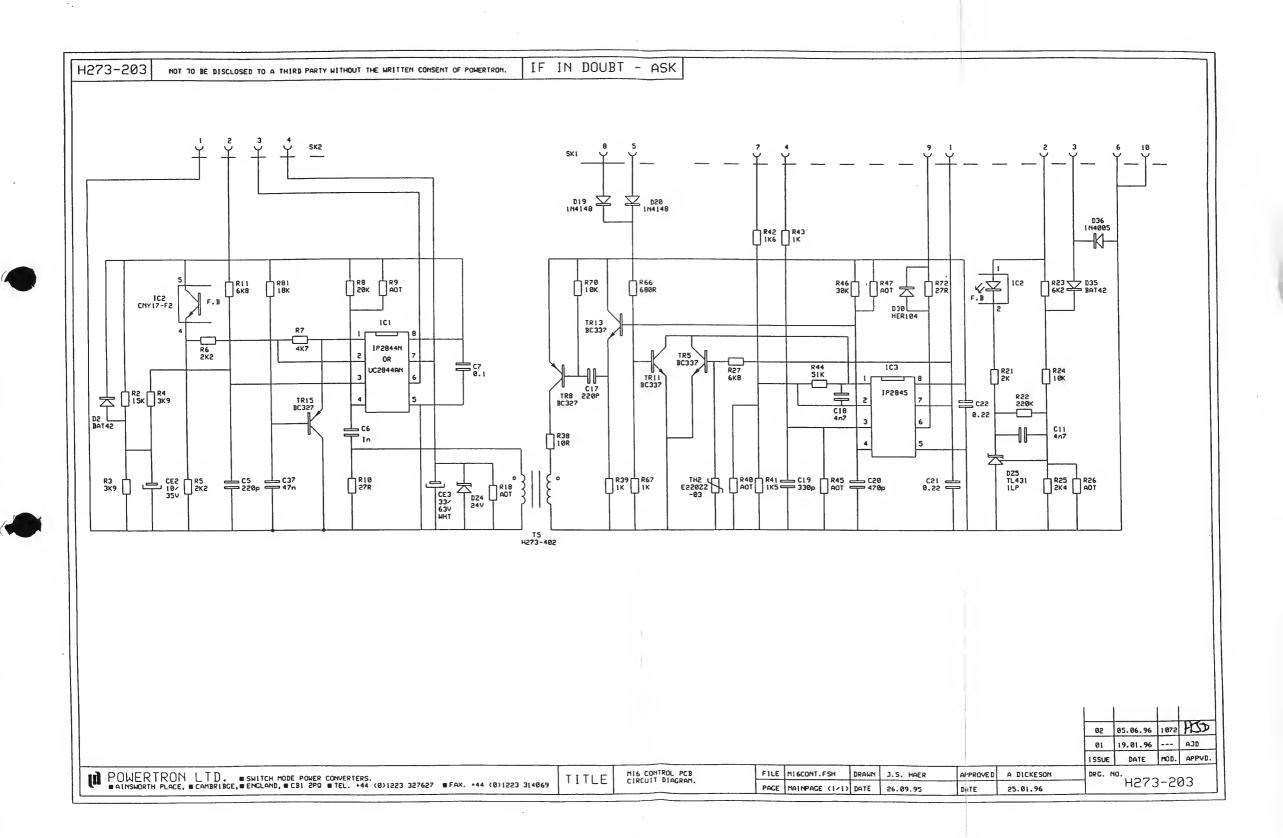

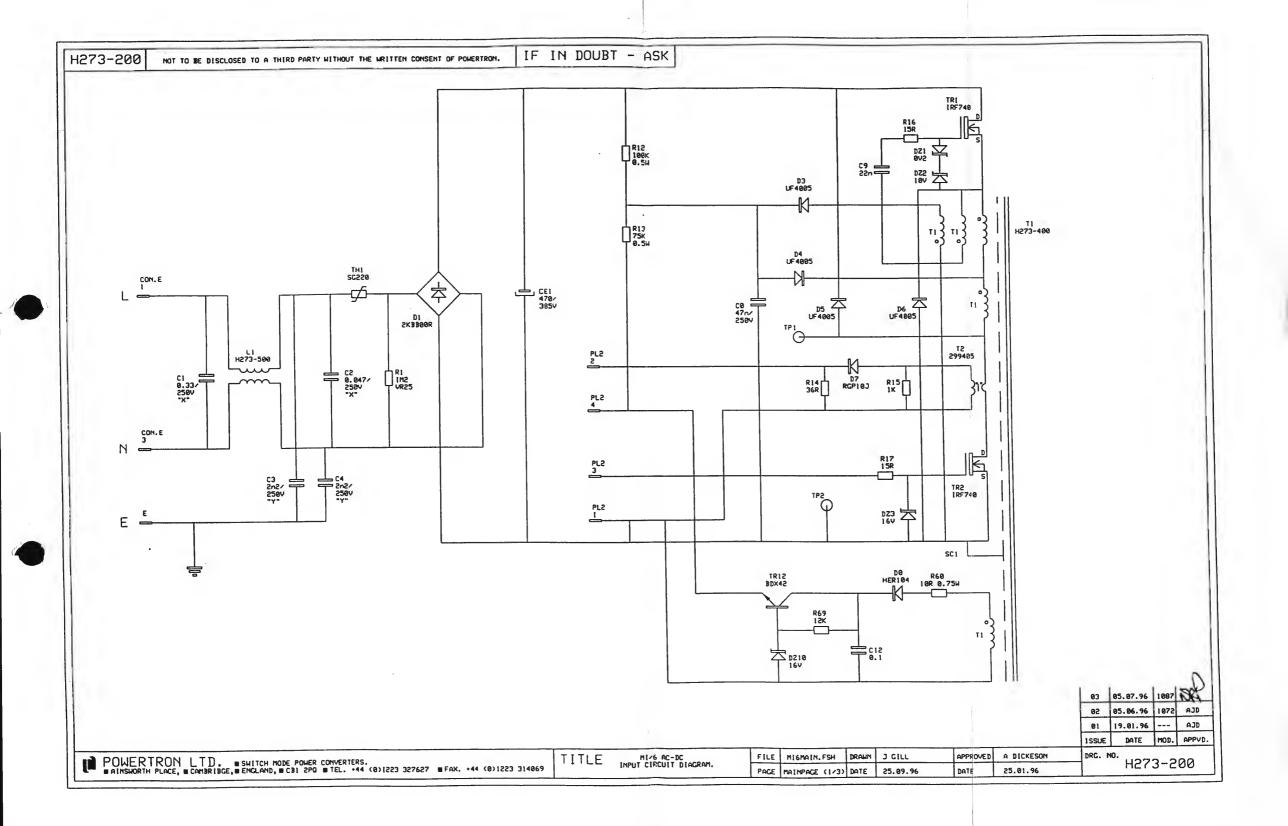

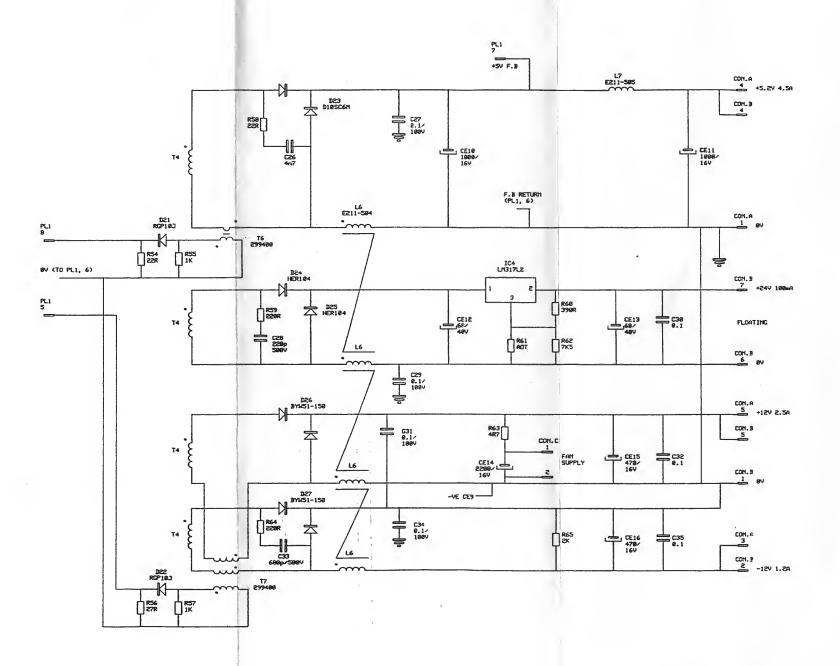

| AC/DC power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |                                                |      |

| Fig. 1-1   Signal generator block schematic   1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | AC/DC pow       | ver supply                                     | 1-39 |

| Fig. 1-1   Signal generator block schematic   1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |                                                |      |

| Fig. 1-2       100 MHz phase locked loop       1-9         Fig. 1-3       Frequency synthesis       1-11         Fig. 1-4       FM/φM drive       1-14         Fig. 1-5       Frequency band selection       1-17         Fig. 1-6       Microprocessor and control block diagram       1-29         Fig. 1-7       Frequency standard selection       1-36         Fig. 1-8       Block diagram of AC/DC power supply module       1-40         List of tables         Table 1-1:       Carrier generation       1-8         Table 1-2:       Attenuator board identification       1-12         Table 1-3:       Attenuator control settings       1-13         Table 1-4:       Frequency band selection       1-16         Table 1-4:       Frequency band selection       1-16         Table 1-5:       Attenuator selection       1-18         Table 1-6:       Interrupts and chip selects       1-30         Table 1-7:       Memory bank addressing       1-30         Table 1-8:       Interrupt lines       1-32         Table 1-9:       Latch control lines       1-33         Table 1-10:       Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | List of figures |                                                |      |

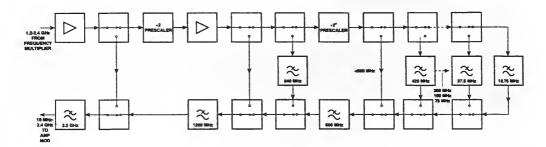

| Fig. 1-2       100 MHz phase locked loop       1-9         Fig. 1-3       Frequency synthesis       1-11         Fig. 1-4       FM/φM drive       1-14         Fig. 1-5       Frequency band selection       1-17         Fig. 1-6       Microprocessor and control block diagram       1-29         Fig. 1-7       Frequency standard selection       1-36         Fig. 1-8       Block diagram of AC/DC power supply module       1-40         List of tables         Table 1-1:       Carrier generation       1-8         Table 1-2:       Attenuator board identification       1-12         Table 1-3:       Attenuator control settings       1-13         Table 1-4:       Frequency band selection       1-16         Table 1-4:       Frequency band selection       1-16         Table 1-5:       Attenuator selection       1-18         Table 1-6:       Interrupts and chip selects       1-30         Table 1-7:       Memory bank addressing       1-30         Table 1-8:       Interrupt lines       1-32         Table 1-9:       Latch control lines       1-33         Table 1-10:       Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Fig. 1-1 Si     | gnal generator block schematic                 | 1-5  |

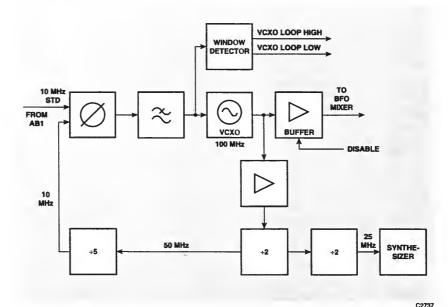

| Fig. 1-3       Frequency synthesis       1-11         Fig. 1-4       FM/φM drive       1-14         Fig. 1-5       Frequency band selection       1-17         Fig. 1-6       Microprocessor and control block diagram       1-29         Fig. 1-7       Frequency standard selection       1-36         Fig. 1-8       Block diagram of AC/DC power supply module       1-40         List of tables         Table 1-1:       Carrier generation       1-8         Table 1-2:       Attenuator board identification       1-12         Table 1-3:       Attenuator control settings       1-13         Table 1-4:       Frequency band selection       1-16         Table 1-4:       Frequency band selection       1-16         Table 1-5:       Attenuator selection       1-18         Table 1-6:       Interrupts and chip selects       1-30         Table 1-7:       Memory bank addressing       1-30         Table 1-8:       Interrupt lines       1-32         Table 1-9:       Latch control lines       1-33         Table 1-10:       Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |                                                |      |

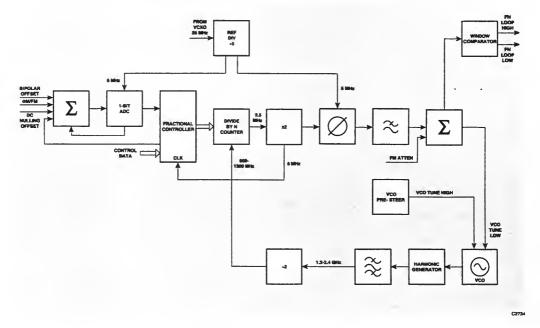

| Fig. 1-4       FM/φM drive       1-14         Fig. 1-5       Frequency band selection       1-17         Fig. 1-6       Microprocessor and control block diagram       1-29         Fig. 1-7       Frequency standard selection       1-36         Fig. 1-8       Block diagram of AC/DC power supply module       1-40         List of tables         Table 1-1:       Carrier generation       1-8         Table 1-2:       Attenuator board identification       1-12         Table 1-3:       Attenuator control settings       1-13         Table 1-4:       Frequency band selection       1-16         Table 1-4:       Frequency band selection       1-16         Table 1-5:       Attenuator selection       1-18         Table 1-6:       Interrupts and chip selects       1-30         Table 1-7:       Memory bank addressing       1-30         Table 1-8:       Interrupt lines       1-32         Table 1-9:       Latch control lines       1-33         Table 1-10:       Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Fig. 1-3 Fr     | requency synthesis                             | 1-11 |

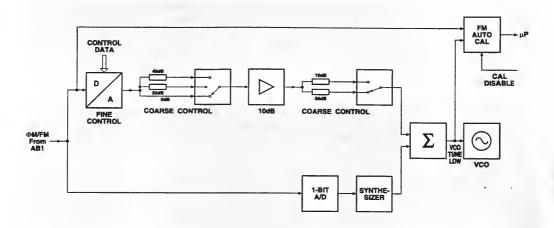

| Fig. 1-5       Frequency band selection       1-17         Fig. 1-6       Microprocessor and control block diagram       1-29         Fig. 1-7       Frequency standard selection       1-36         Fig. 1-8       Block diagram of AC/DC power supply module       1-40         List of tables         Table 1-1: Carrier generation       1-8         Table 1-2: Attenuator board identification       1-12         Table 1-3: Attenuator control settings       1-13         Table 1-4: Frequency band selection       1-16         Table 1-5: Attenuator selection       1-16         Table 1-6: Interrupts and chip selects       1-30         Table 1-7: Memory bank addressing       1-30         Table 1-8: Interrupt lines       1-32         Table 1-9: Latch control lines       1-33         Table 1-10: Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Fig. 1-4 F      | M/φM drive                                     | 1-14 |

| Fig. 1-6       Microprocessor and control block diagram       1-29         Fig. 1-7       Frequency standard selection       1-36         Fig. 1-8       Block diagram of AC/DC power supply module       1-40         List of tables         Table 1-1: Carrier generation       1-8         Table 1-2: Attenuator board identification       1-12         Table 1-3: Attenuator control settings       1-13         Table 1-4: Frequency band selection       1-16         Table 1-5: Attenuator selection       1-18         Table 1-6: Interrupts and chip selects       1-30         Table 1-7: Memory bank addressing       1-30         Table 1-8: Interrupt lines       1-32         Table 1-9: Latch control lines       1-33         Table 1-10: Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Fig. 1-5 Fr     | requency hand selection                        | 1-17 |

| Fig. 1-7       Frequency standard selection       1-36         Fig. 1-8       Block diagram of AC/DC power supply module       1-40         List of tables         Table 1-1: Carrier generation       1-8         Table 1-2: Attenuator board identification       1-12         Table 1-3: Attenuator control settings       1-13         Table 1-4: Frequency band selection       1-16         Table 1-5: Attenuator selection       1-18         Table 1-6: Interrupts and chip selects       1-30         Table 1-7: Memory bank addressing       1-30         Table 1-8: Interrupt lines       1-32         Table 1-9: Latch control lines       1-33         Table 1-10: Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Fig. 1-6 M      | icroprocessor and control block diagram        | 1_20 |

| Fig. 1-8 Block diagram of AC/DC power supply module       1-40         List of tables         Table 1-1: Carrier generation       1-8         Table 1-2: Attenuator board identification       1-12         Table 1-3: Attenuator control settings       1-13         Table 1-4: Frequency band selection       1-16         Table 1-5: Attenuator selection       1-18         Table 1-6: Interrupts and chip selects       1-30         Table 1-7: Memory bank addressing       1-30         Table 1-8: Interrupt lines       1-32         Table 1-9: Latch control lines       1-33         Table 1-10: Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                                                |      |

| List of tables         Table 1-1:       Carrier generation       1-8         Table 1-2:       Attenuator board identification       1-12         Table 1-3:       Attenuator control settings       1-13         Table 1-4:       Frequency band selection       1-16         Table 1-5:       Attenuator selection       1-18         Table 1-6:       Interrupts and chip selects       1-30         Table 1-7:       Memory bank addressing       1-30         Table 1-8:       Interrupt lines       1-32         Table 1-9:       Latch control lines       1-33         Table 1-10:       Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Fig 1-8 B       | lock diagram of AC/DC power supply module      | 1 40 |

| Table 1-1:       Carrier generation       1-8         Table 1-2:       Attenuator board identification       1-12         Table 1-3:       Attenuator control settings       1-13         Table 1-4:       Frequency band selection       1-16         Table 1-5:       Attenuator selection       1-18         Table 1-6:       Interrupts and chip selects       1-30         Table 1-7:       Memory bank addressing       1-30         Table 1-8:       Interrupt lines       1-32         Table 1-9:       Latch control lines       1-33         Table 1-10:       Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 116.10 2        | ook diagram of NGDC power supply module        | 1-40 |

| Table 1-2:       Attenuator board identification       1-12         Table 1-3:       Attenuator control settings       1-13         Table 1-4:       Frequency band selection       1-16         Table 1-5:       Attenuator selection       1-18         Table 1-6:       Interrupts and chip selects       1-30         Table 1-7:       Memory bank addressing       1-30         Table 1-8:       Interrupt lines       1-32         Table 1-9:       Latch control lines       1-33         Table 1-10:       Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | List of tables  |                                                |      |

| Table 1-3:       Attenuator control settings       1-13         Table 1-4:       Frequency band selection       1-16         Table 1-5:       Attenuator selection       1-18         Table 1-6:       Interrupts and chip selects       1-30         Table 1-7:       Memory bank addressing       1-30         Table 1-8:       Interrupt lines       1-32         Table 1-9:       Latch control lines       1-33         Table 1-10:       Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 1-1:      | Carrier generation                             | 1-8  |

| Table 1-3:       Attenuator control settings       1-13         Table 1-4:       Frequency band selection       1-16         Table 1-5:       Attenuator selection       1-18         Table 1-6:       Interrupts and chip selects       1-30         Table 1-7:       Memory bank addressing       1-30         Table 1-8:       Interrupt lines       1-32         Table 1-9:       Latch control lines       1-33         Table 1-10:       Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 1-2:      | Attenuator board identification                | 1-12 |

| Table 1-4:       Frequency band selection       1-16         Table 1-5:       Attenuator selection       1-18         Table 1-6:       Interrupts and chip selects       1-30         Table 1-7:       Memory bank addressing       1-30         Table 1-8:       Interrupt lines       1-32         Table 1-9:       Latch control lines       1-33         Table 1-10:       Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 1-3:      |                                                |      |

| Table 1-5:       Attenuator selection       1-18         Table 1-6:       Interrupts and chip selects       1-30         Table 1-7:       Memory bank addressing       1-30         Table 1-8:       Interrupt lines       1-32         Table 1-9:       Latch control lines       1-33         Table 1-10:       Buffered chip selects       1-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Table 1-4:      | Frequency band selection                       | 1-16 |